采样点是节点判断信号逻辑电平的位置,对CAN/CAN FD总线来说极其重要,尤其是在组网的时候,多个节点要尽量保持同一个采样点。若网络中节点采样点不一致可能会导致同样的采样频率出现采样错误,进而使整个网络出现故障,所以对CAN/CAN FD节点进行采样点的测试显得尤为重要,采样点测试目的用于检查DUT(Device Under Test)的采样点设置是否遵守规范要求。本文以CANoe自带的采样点测试工程为例介绍如何基于VH6501(CAN/CAN FD总线干扰仪)进行CAN/CAN FD采样点测试。

1、测试原理

采样点的位置不受DUT所处的收发状态影响,故针对采样点测试既可以干扰DUT发送的指定报文的某个位,也可以通过测试工具发送特定干扰报文去检测DUT的行为。

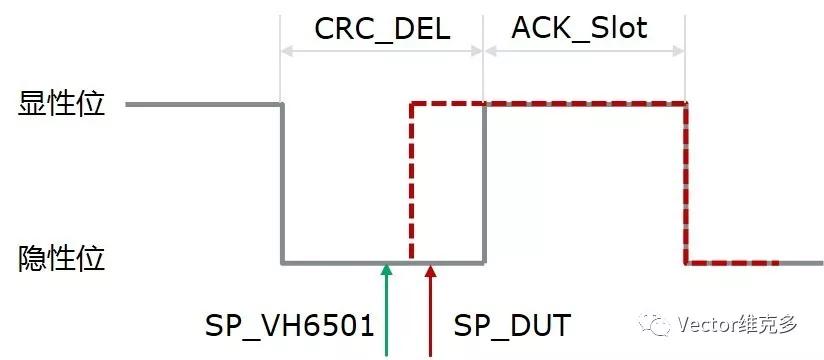

本文描述的采样点测试案例中被测节点扮演的是接收节点的角色。以CAN采样点测试为例,VH6501在检测到总线空闲时,发送较高优先级的特定干扰报文,完成一个干扰循环。每次干扰循环发送结束,微调CRC Delimiter位(隐性位)长度,使其逐次缩短,导致后一位ACK Slot(显性位)前移,并将ACK Slot长度增加,保证整帧报文的长度不变。当显性位电平由后往前,移至DUT采样点位置,会被DUT采到并判定CRC Delimiter位为高电平,出现格式错误,DUT随即发送错误帧,并被CANoe采集到。

测试时需要将CANoe逻辑通道(VH6501所在通道)的采样点选取尽量靠前,避免VH6501本身先被干扰到而报错。另外,每次干扰循环结束,VH6501会发送一定数目的正常报文,使DUT始终保持在Error Active状态,该状态下发送的主动错误帧容易被识别。

图1 VH6501干扰示意图

2、CAN 采样点测试实现过程

软件配置

将VH6501通道分配给软件通道CAN1,在图2所示界面设置Mode为CAN,并勾选Activate选项使能VH6501总线干扰功能。

图2 分配VH6501通道并使能干扰功能

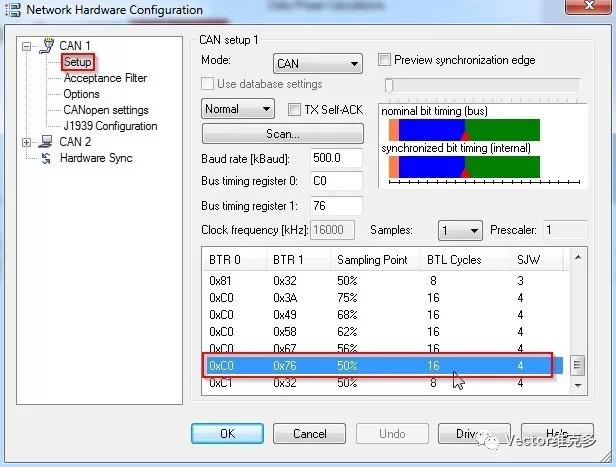

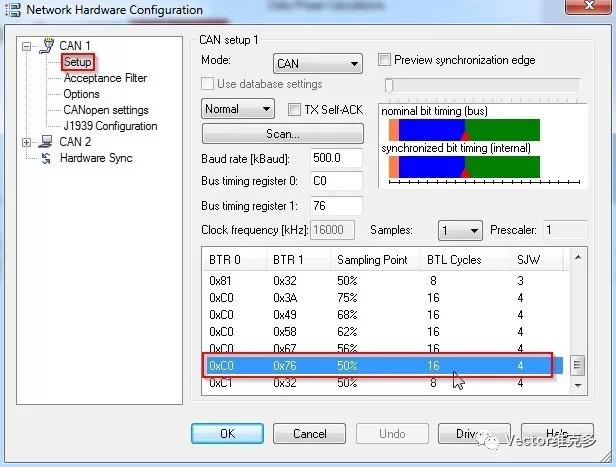

VH6501的采样点设置尽量靠前,确保优先干扰到DUT的采样点,BTL Cycles和SJW选择数值较大的组合,可参考图3配置:

图3 配置VH6501采样点及SJW数值

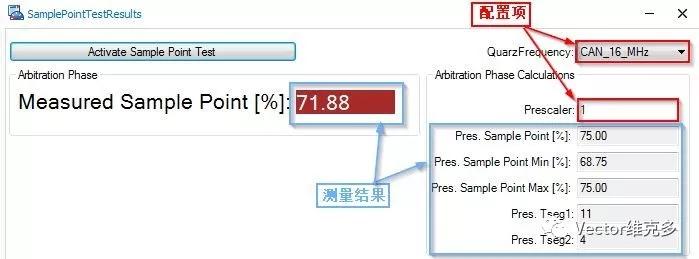

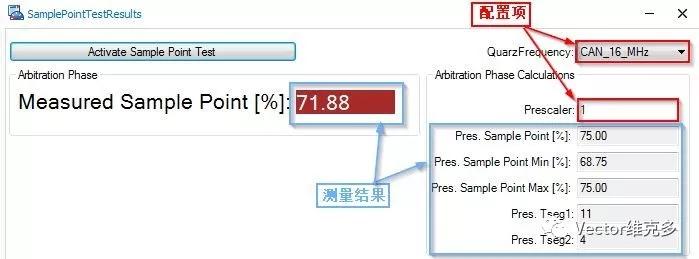

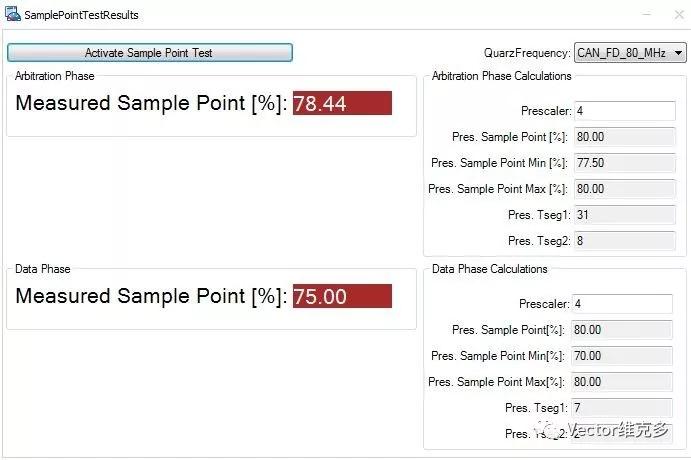

在Panel窗口配置被测DUT的时钟频率和预分频(Prescaler)参数,完成后直接点击Active Sample Point Test,即可得到测量结果,如图4所示:

图4 配置DUT时钟频率和预分频,获得测量结果

其中,71.88%的测量结果是VH6501逐步缩短CRC Delimiter位至该位宽度为230ticks(500K通讯速率下标称位宽度为320ticks)时DUT报错,即表明干扰到DUT采样点,计算230/320得到。右侧的计算结果是根据DUT采用的时钟频率、预分频值考虑了DUT标称位宽度的TQ数量后,经过换算得到其采样点位置在68.75%~75%之间。

代码实现

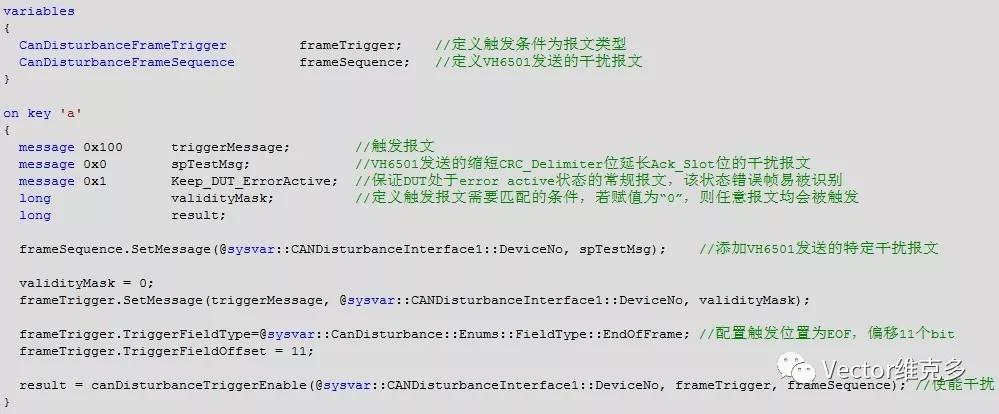

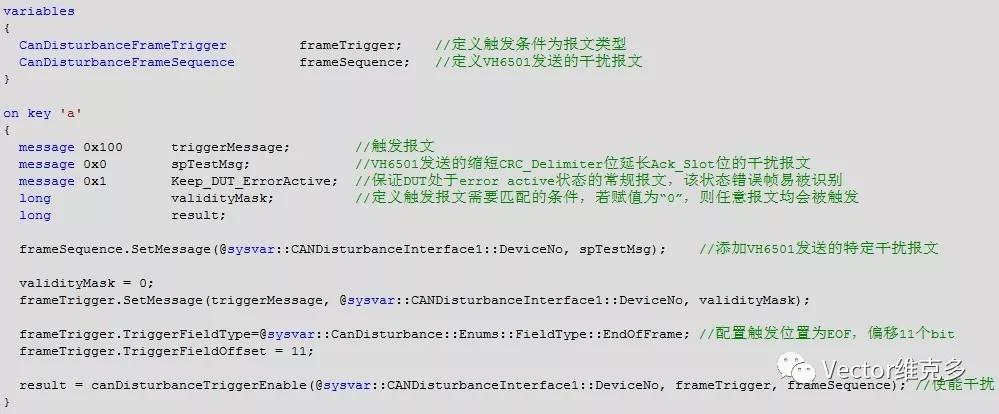

代码的核心是如何通过VH6501按照一定的步长逐步缩短和延长一个位的长度。

VH6501采用的是160M的时钟频率,对应每个tick的宽度是6.25ns,单次可调整的位宽度精度为1个tick。以CAN总线采用的500KBaud速率为例,一个位宽度为2000ns,由320个tick组成。部分代码原理示意如下:

- 配置VH6501的触发方式、触发位置以及干扰序列,并使能干扰

图5 测试代码部分1

- 缩短CRC Delimiter位和Ack Slot位的延长

图6 测试代码部分2

3、CAN FD 采样点测试实现过程

CAN FD的采样点测试相比CAN要更加复杂,因为CAN FD涉及到传输速率的切换,需要分别测试CAN FD报文仲裁段以及数据段的采样点,而不同整车厂对于这两段采样点位置测试的规范都有不同定义,主要区别在于干扰位置选择不同。采样点测试中干扰位置最好选择一帧报文“隐性位”→“显性位”→“隐性位”序列中的“显性位”,ISO 11898-1中规定在逻辑电平由隐性到显性的跳变沿会进行重同步,一般来说在此处跳变沿会位于同步段(Sync Segment)。

本示例在CAN FD仲裁段采样点测试中,通过将干扰报文的BRS位设置为“0”,此时整帧报文传输速率与仲裁段一致,选取干扰报文CRC场中的最佳干扰位施加干扰;对数据段采样点测试则将干扰报文的BRS位置为“1”,此时报文数据段部分会进行波特率切换,同样的在CRC场选择合适的最佳干扰位施加干扰。

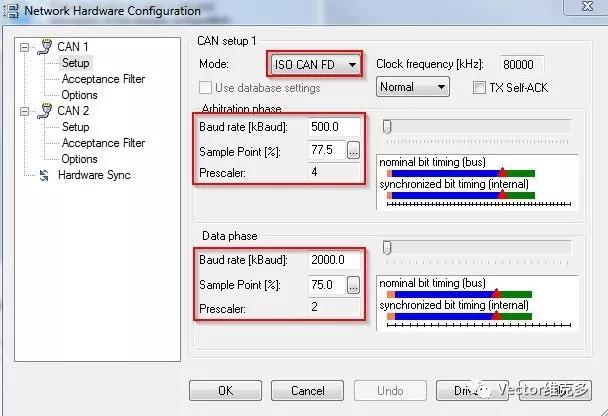

以下是CAN FD采样点测试过程的简要配置:

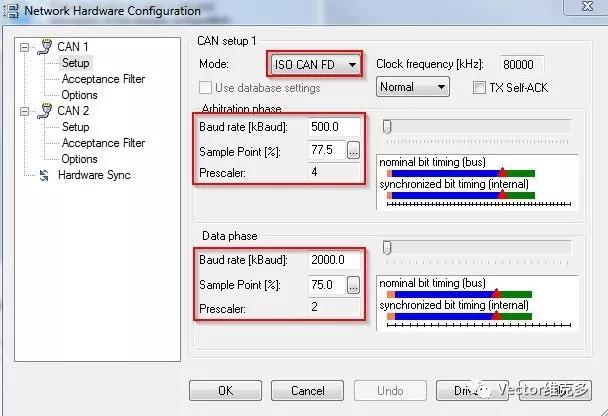

将Mode切换到CAN FD,并且由于涉及到波特率切换,若采样点数值设置偏差过大的话可能导致通信错误,采样点的设置除了需要比DUT靠前,还需要与被测DUT的采样点尽量接近。

图7 VH6501采样点参数配置

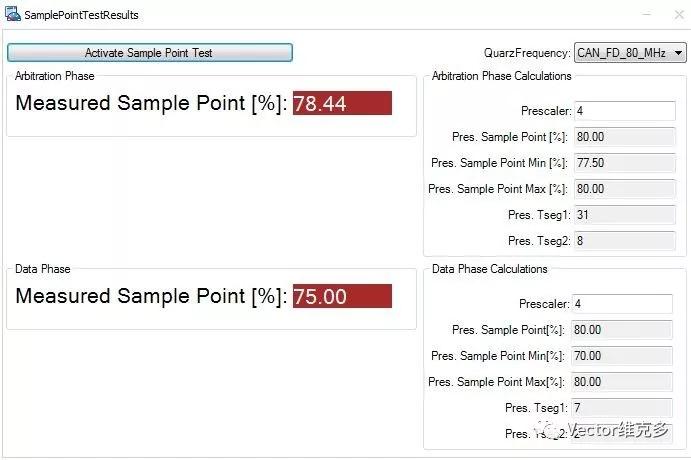

在Panel窗口中配置时钟频率以及数据段和仲裁段的预分频值,完成后开始测量即可得到结果如图8所示,实际DUT的仲裁段和数据段采样均配置为80%。

图8 CAN FD采样点测试结果

当然,干扰DUT发送的报文也是可行的。但在这种情况下,指定干扰的位则很可能不是最佳干扰位。

4、误差分析

采样点的测试结果受到很多因素影响,下面列举几个主要误差来源:

> 标称位宽度的TQ数

上文提到采样点测试最佳干扰位置是“隐性位”→“显性位”→“隐性位”序列中的“显性位”,ISO 11898-1协议规定重同步会使跳变沿落在同步段里,但是协议并未明确定义跳变沿具体落在同步段(1个TQ宽度)的位置,所以由DUT自身带来最大误差为1个TQ,而TQ数量与DUT采用的时钟、预分频值以及传输波特率等都相关。

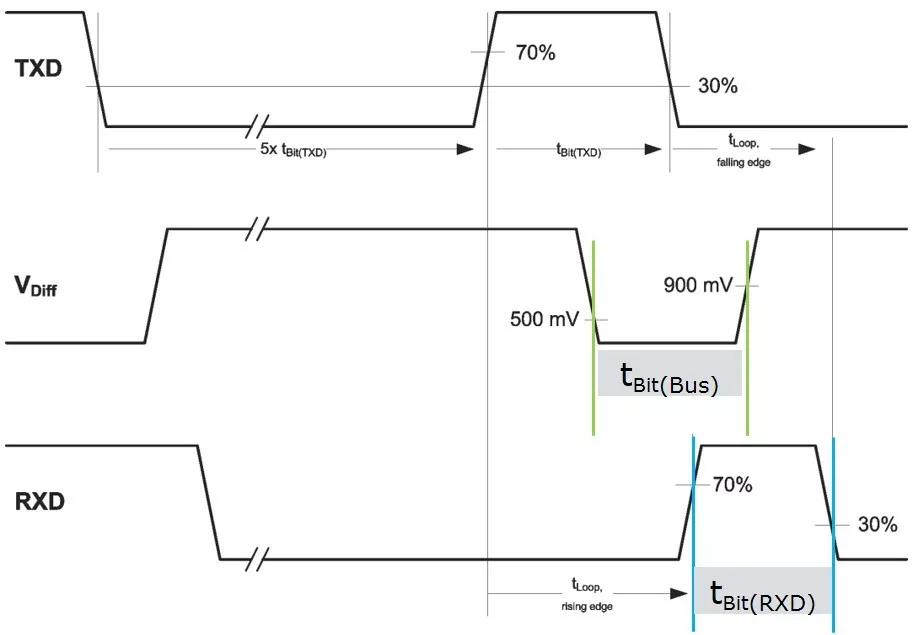

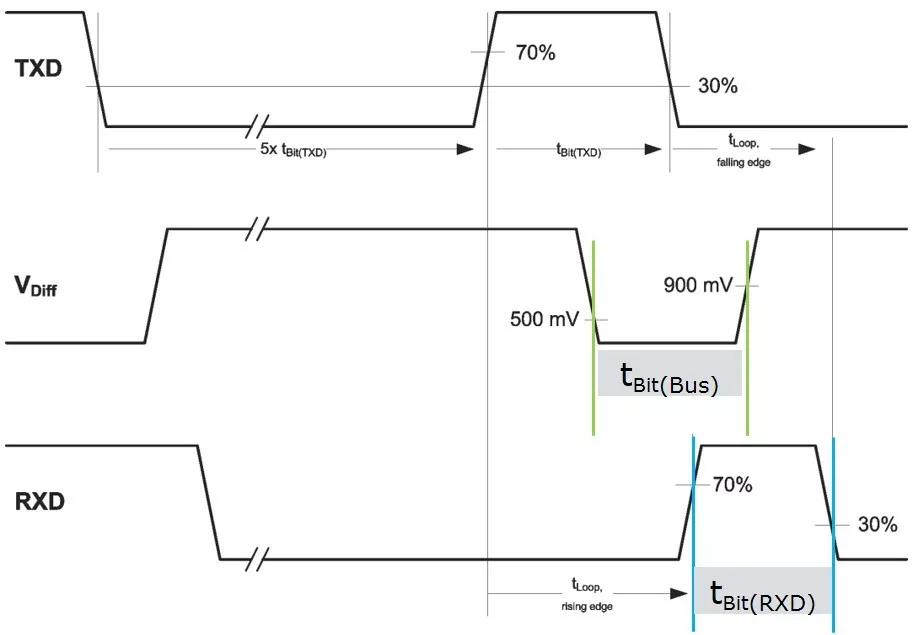

> 总线传输的影响

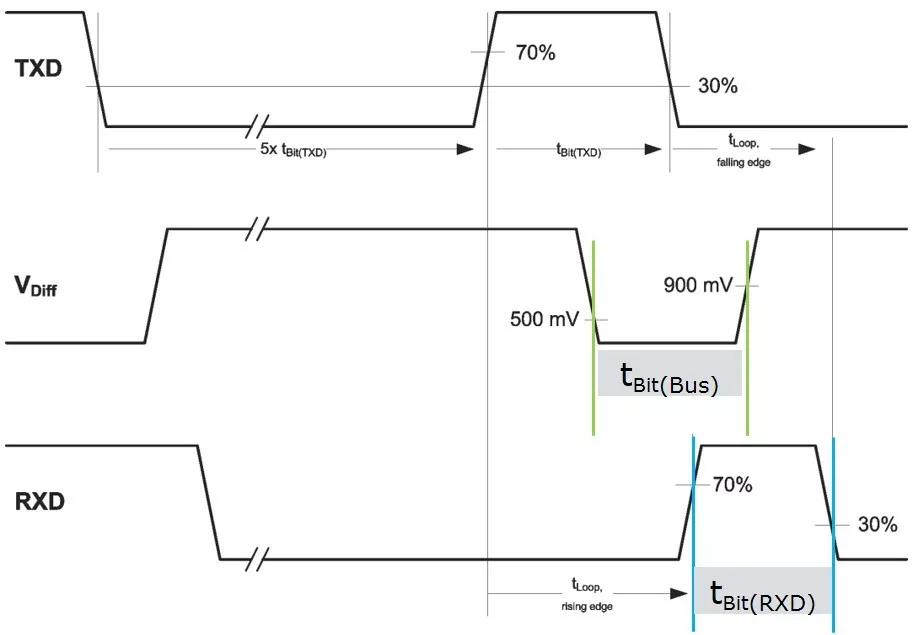

图9展示了信号传输过程中的位时序过程,tbit(bus)是指总线上一个位的电平长度,tbit(RXD)是指DUT内部主控芯片RXD引脚检测到的一个位电平长度。

在ISO 11898-2:2015中有定义ΔtRec的数值范围,总线传输速率在1Mbit/s~2Mbit/s内,ΔtRec误差在-65ns~+40ns之间,传输速率在2Mbit/s~5Mbit/s内,ΔtRec误差在-45ns~+15ns之间。以2Mbit/s为例,位时间长度为500ns,此时在RXD引脚上的位时间长度会比总线上的位时间长度短13%或长8%。

图9 总线信号与RXD引脚信号位时间示意图

> 测试工具VH6501精度的影响

VH6501的测量精度是指VH6501在每次干扰循环可缩短或增长的步进长度,即6.25ns,称之为ΔtMesHW。

下面通过两个示例看下这几个误差源的影响。

例1:

假设CAN时钟频率为80MHz,预分频值为1,则单个TQ长度ΔtTQ为12.5ns,ΔtMesHW为6.25ns。仲裁段传输速率为500kBaud,数据段为2MBaud,ΔtRec取25ns,所以ΔtRec带来的误差在仲裁段为1.25%,在数据段上升到5%。测试工具VH6501步进长度ΔtMesHW所带来的误差在仲裁段和数据段分别为0.3125%和1.25%。再加上由同步跳变沿所处的位置不确定,在仲裁段和数据段中带来的最大误差分别为0.625%和2.5%。由此,在仲裁段中总的最大误差为 2.1875%(1.25% + 0.3125% + 0.625%),在数据段中总的最大误差为8.75%(5% + 1.25% + 2.5%)。

例2:

若预分频值在仲裁段设为4,数据段设为5,其他数据同例1。则最直观的表现为单个TQ长度会增加,在仲裁段中ΔtTQ1为50ns,由ΔtTQ1带来的误差为2.5%。同理在数据段中ΔtTQ2带来的误差为12.5%。这两者带来的误差已经超过了ΔtRec所带来的误差,因此ΔtRec的影响可以忽略。

由此,在仲裁段中总的最大误差为2.8125%(0.3125%+2.5%),在数据段中总的最大误差为 13.75%(1.25%+12.5%)。所以若理论采样点为75%,实际测试得到的结果,仲裁段在75%±2.8125%,数据段在75%±13.75%范围内都是合理的。

综上,如果在测试环境中DUT所采用时钟对应的最小TQ时间长度在ΔtRec范围内,并且实际TQ配置在此范围内,则在采样点测试结果中需要考虑ΔtRec带来的误差。通过上述例子可以看出VH6501所带来的误差占比是很小的,大部分是由于CAN协议本身所带来的误差。这些误差可以认为是合理且无法避免的,在实际测试验证中需要进行一定的考量。

备注:

[1]. CANoe 11.0及以上版本中提供适用于CAN/CAN FD采样点测试的例程“CANDisturbance_Sample_Point_Test.cfg”,本文提到的测试方法均是基于该例程,如果需要完整测试代码,请在该工程中查看。

广告

广告