SoC,系统级芯片,汽车系统级SoC主要面向两个领域,一是座舱,二是智能驾驶,这两者的界限现在正变得越来越模糊。随着汽车电子架构的演进,新出现了网关SoC,典型代表NXP的S32G274A。通常网关SoC不需要太强算力,不过S32G274A有4个Cortex-A53内核,达到低端座舱的水准。

Orin是一个典型的智能驾驶SoC,包含存储管理、外围、CPU、GPU和加速器。CPU、GPU、AI加速器以及连接子系统的总线或片上网络(NoC)是SoC的核心,因此本连载将对应这四个部分分四个章节带大家深入了解汽车SoC。目录如下:

1.5、目前与未来常见座舱与智能驾驶SoC算力统计

2.3、冯诺伊曼架构Von Neumann Architecture

2.4、哈佛架构 Harvard Architecture

2.16、特斯拉座舱用AMD Zen2 CPU微架构分析

2.17、汽车功能安全的关键:ARM的多核调度DSU

3.4、GPU的CPU开销即Draw Call驱动开销

5.2、NoC(Network on Chip)片上网络

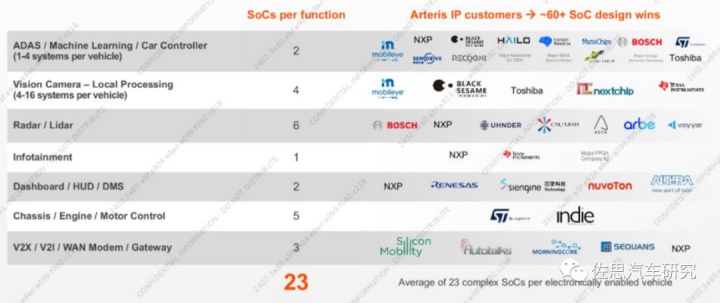

5.4、汽车SoC的NoC IP霸主供应商——Arteris

广义而言,汽车领域算力稍强(2K DMIPS以上)的MCU都可算是SoC。

上图是SoC IP供应商Arteris 的IPO材料,Arteris认为平均每辆车有23个SoC。

-

至少一个微处理器(MPU)或数字信号处理器(DSP),但也可以有多个处理器内核;

-

存储器可以是RAM、ROM、EEPROM和闪存中的一种或多种;

-

用于提供时间脉冲信号的振荡器和锁相环电路;

-

由计数器和计时器、电源电路组成的外设;

-

不同标准的连线接口,如USB、火线、以太网、通用异步收发和序列周边接口等;

-

电压调理电路及稳压器。

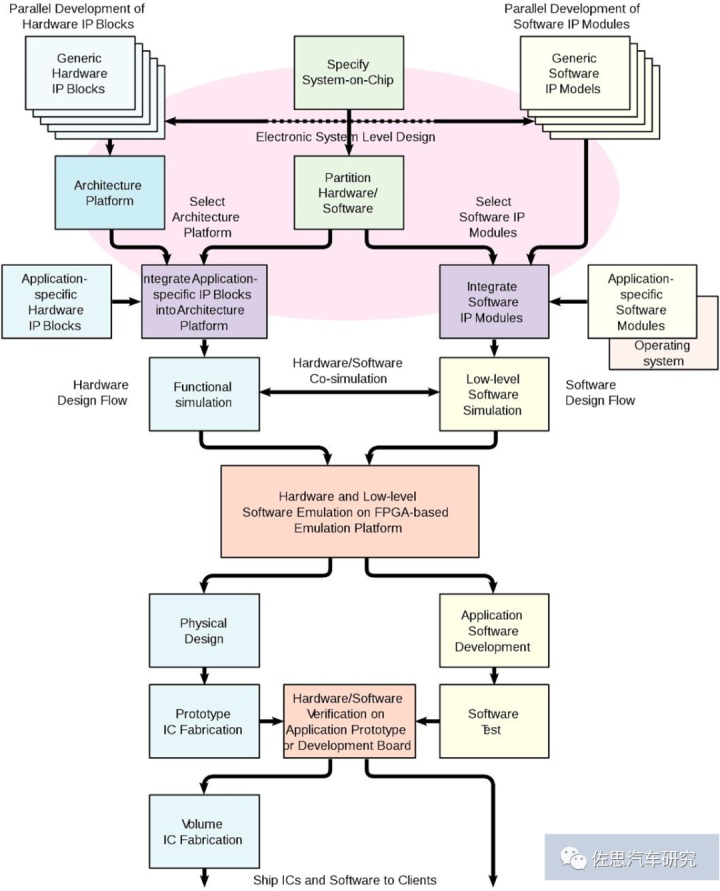

一个完整的系统级芯片由硬件和软件两部分组成,其中软件用于控制硬件部分的微控制器、微处理器或数字信号处理器内核,以及外部设备和接口。系统级芯片的设计流程主要是其硬件和软件的协同设计。

由于系统级芯片的集成度越来越高,设计工程师必须尽可能采取可复用的设计思路。现今大部分SoC都使用预定义的IP核(包括软核、硬核和固核),以可复用设计的方式来完成快速设计。在软件开发方面,协议栈是一个重要的概念,它用来驱动USB等行业标准接口。在硬件设计方面,设计人员通常使用EDA工具将已经设计好(或者购买)的IP核连接在一起,在一个集成开发环境(IDE)下集成各种子功能模块。

芯片设计在被送到晶圆厂进行流片生产之前,设计人员会采取不同方式对其逻辑功能进行验证。仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80% ,采用先进的设计与仿真验证方法已成为SoC设计成功的关键。

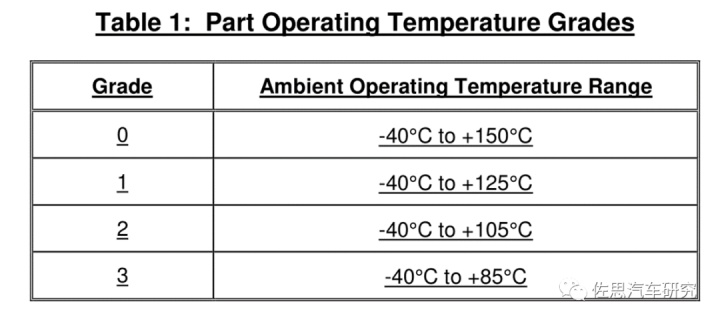

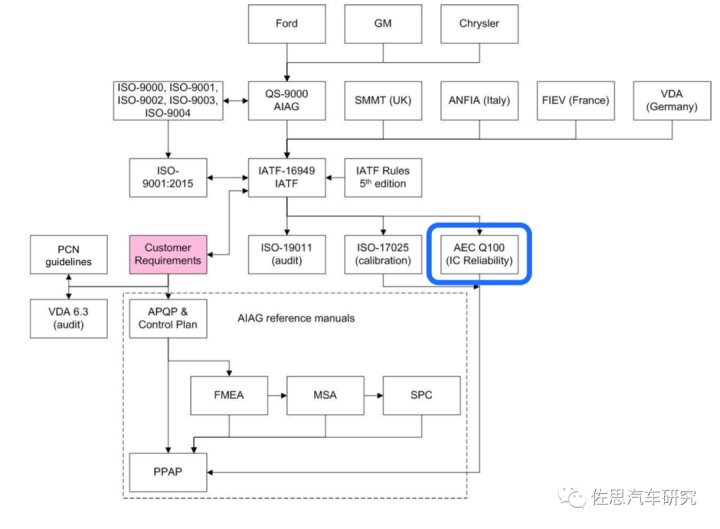

汽车电子委员会(AEC- Automotive Electronics Council)由克莱斯勒(Chrysler) 、福特(Ford) 和通用汽车公司(General Motors)成立,旨在制定电气元件的通用质量标准。第一版AEC标准是1994年推出的,100针对集成电路,101针对分离元件,102针对光电元件,104针对MCM模块,200针对被动元件。

AEC-Q100是使用最广泛最基础的车规级标准,几乎是强制性的标准,功能安全不是强制性标准,只是建议性标准。

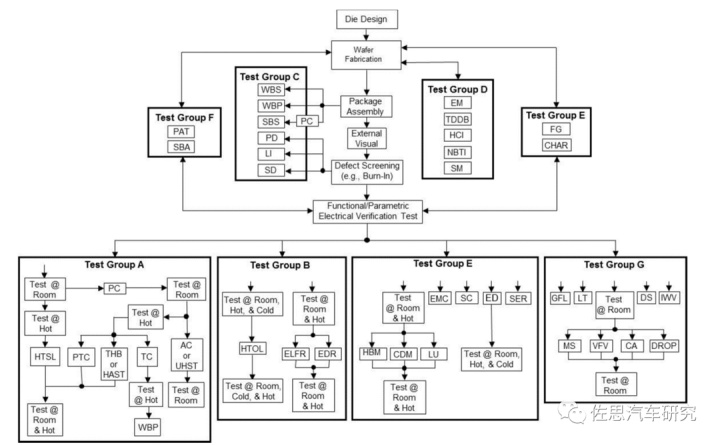

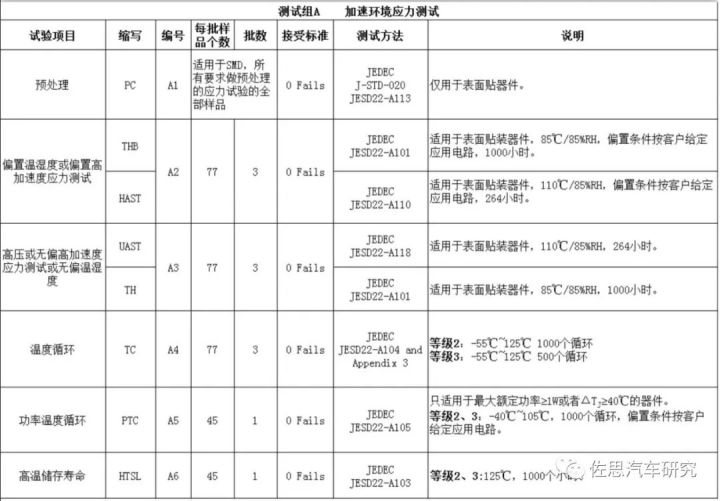

1) AcceleratedEnvironment Stress (加速环境压力)

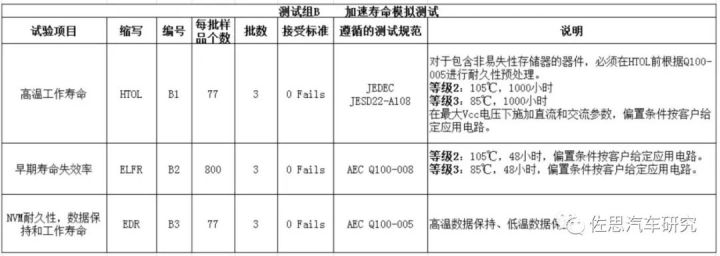

2) Accelerate LifetimeSimulation (加速寿命仿真)

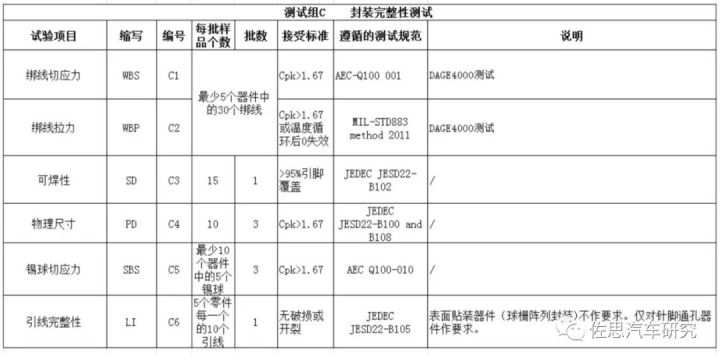

3) Packaging/Assembly (封装/组装)

4) Die Fabrication (芯片制程)

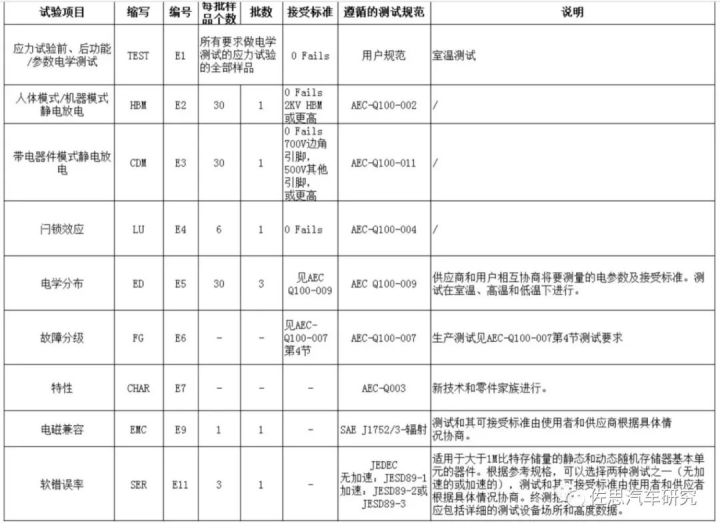

5) ElectricalVerification (电气验证)

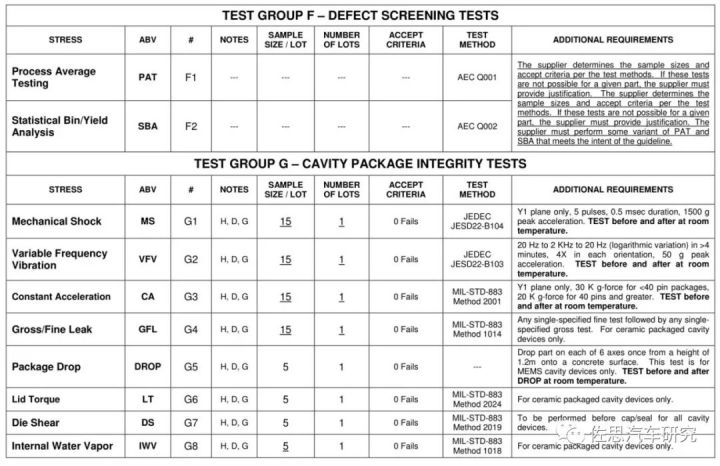

6) Defect Screening (不良品筛选)

7) Cavity PackageIntegrity (腔体封装完整性)

最有意思的是D,没有测试标准和方法,主要是芯片制造领域的测试,可能是因为芯片制造领域变化太快或其他因素,因此AEC-Q100只提出了测试项,分别是电迁移即EM、经介质击穿TDDB、热载流子注入HCI、负偏压温度不稳定性NBTI、压力迁移SM。测试标准和方法是空白,AEC委员会附加说明The data, test method, calculations and internal criteria should beavailable to the user upon request for new technologies.意思就是用户看着办吧。

广告

广告