深入了解汽车系统级芯片SoC连载之七:汽车功能安全的关键:ARM的多核调度DSU

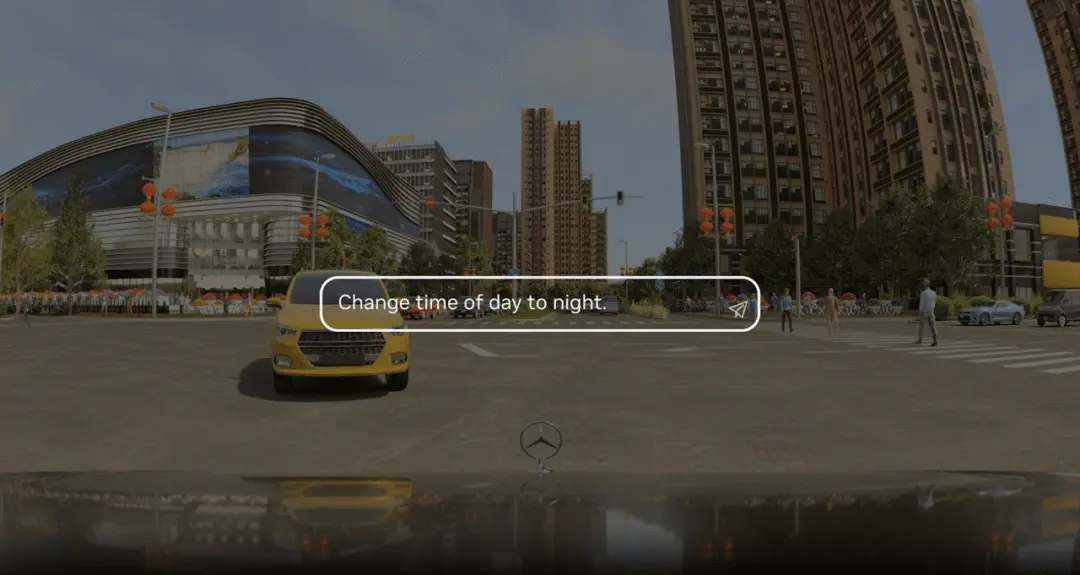

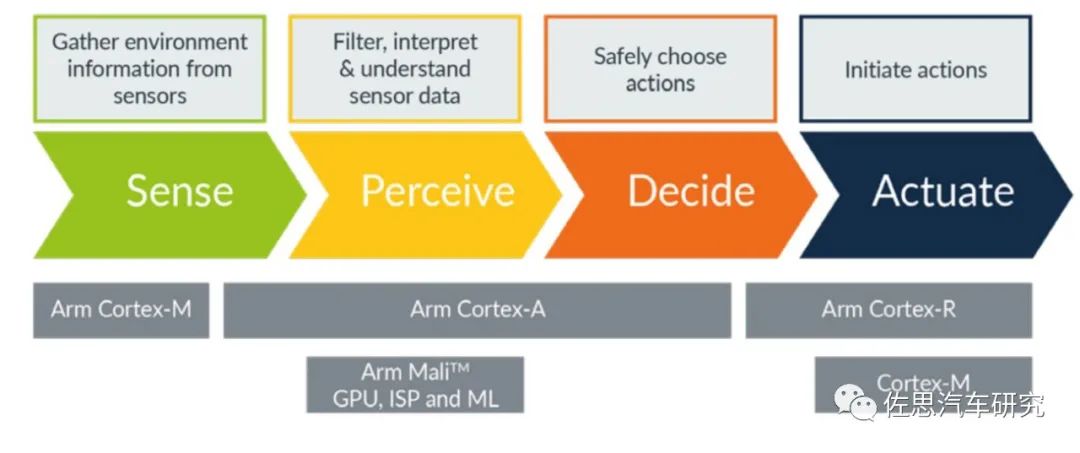

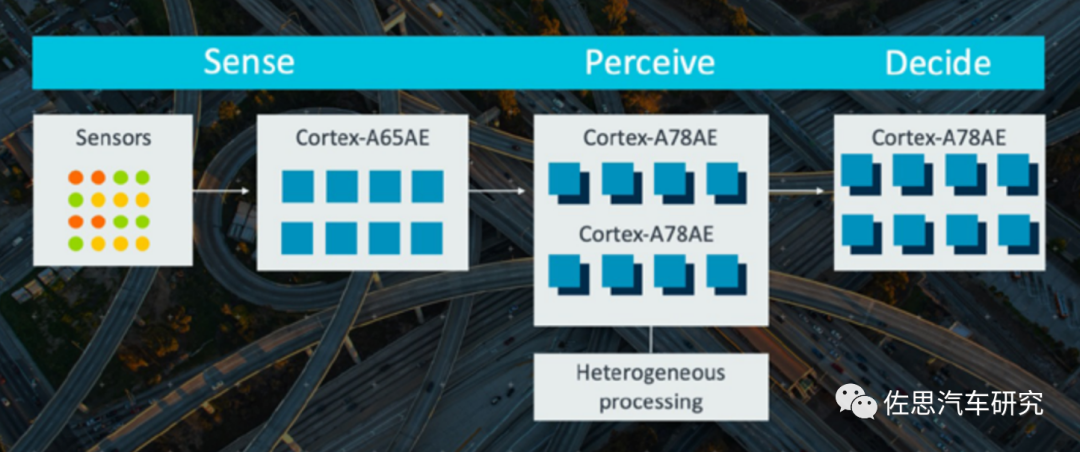

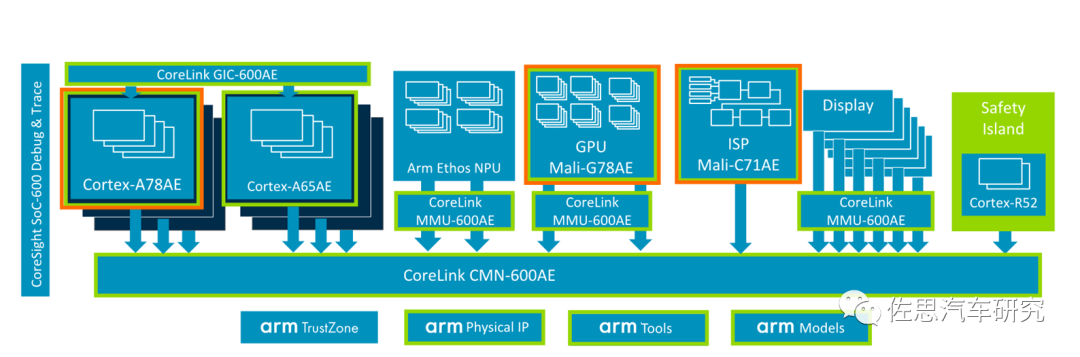

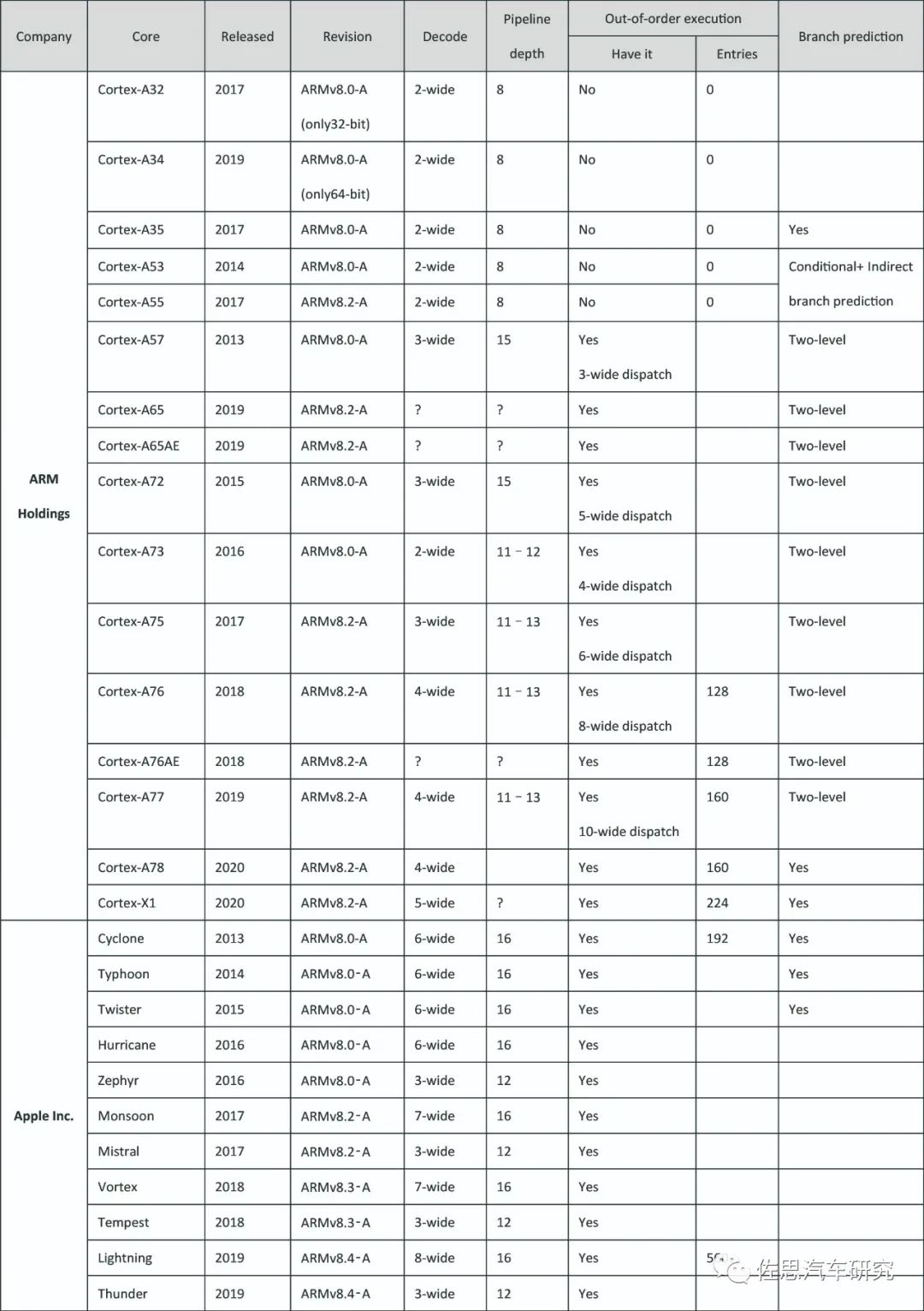

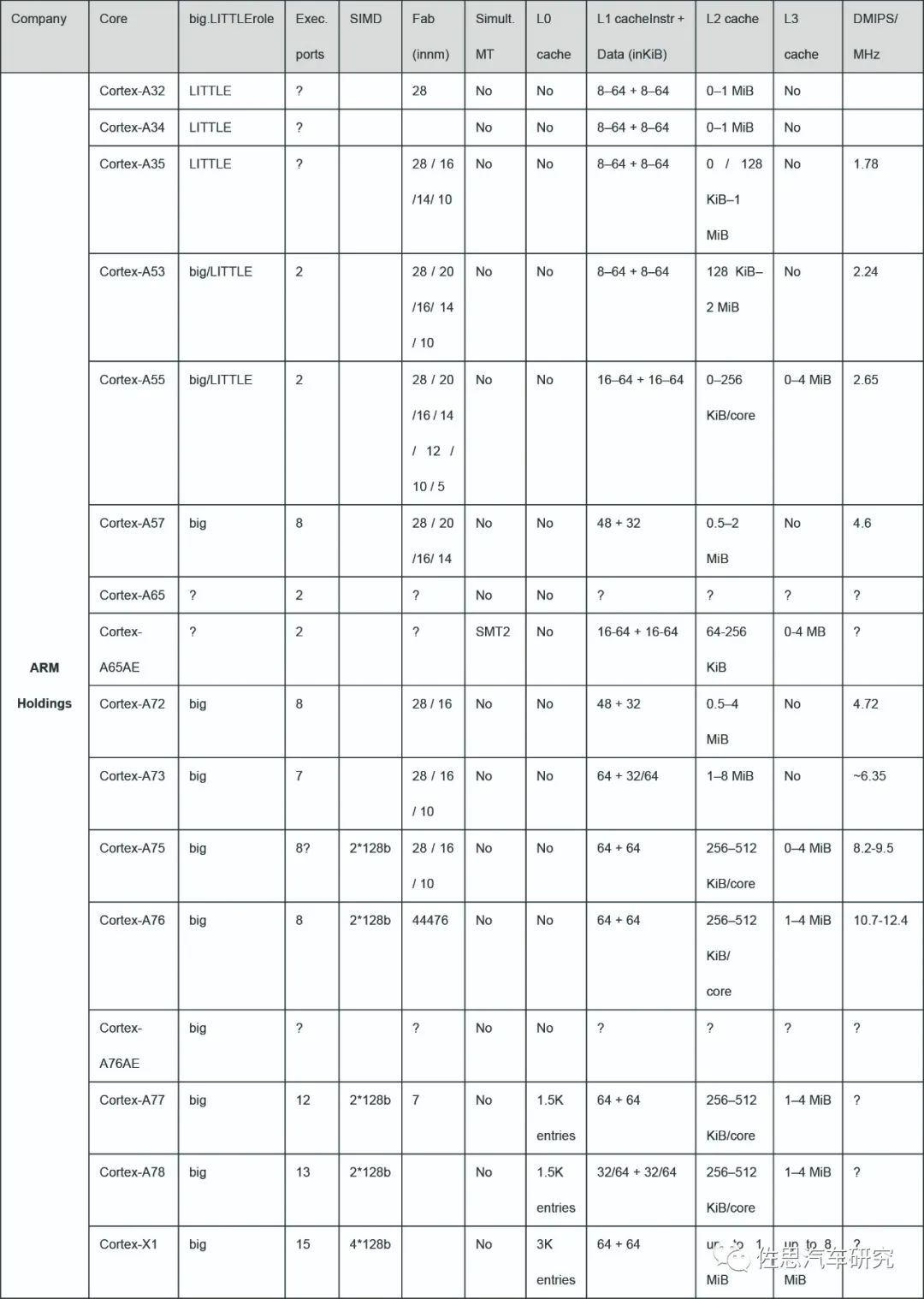

ARM推出一系列针对自动驾驶的CPU架构,均符合汽车功能安全,分别是A65AE、A76AE和A78AE,AE代表汽车级增强。

ARM自动驾驶计算平台配置

图片来源:互联网

ARM针对汽车功能安全的Split/Lock/Hybrid模式

图片来源:互联网

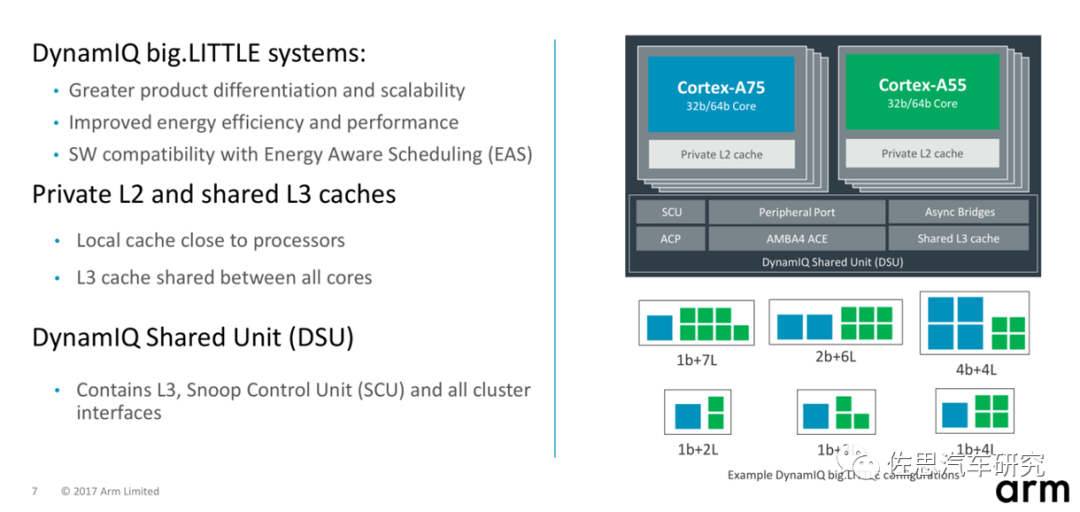

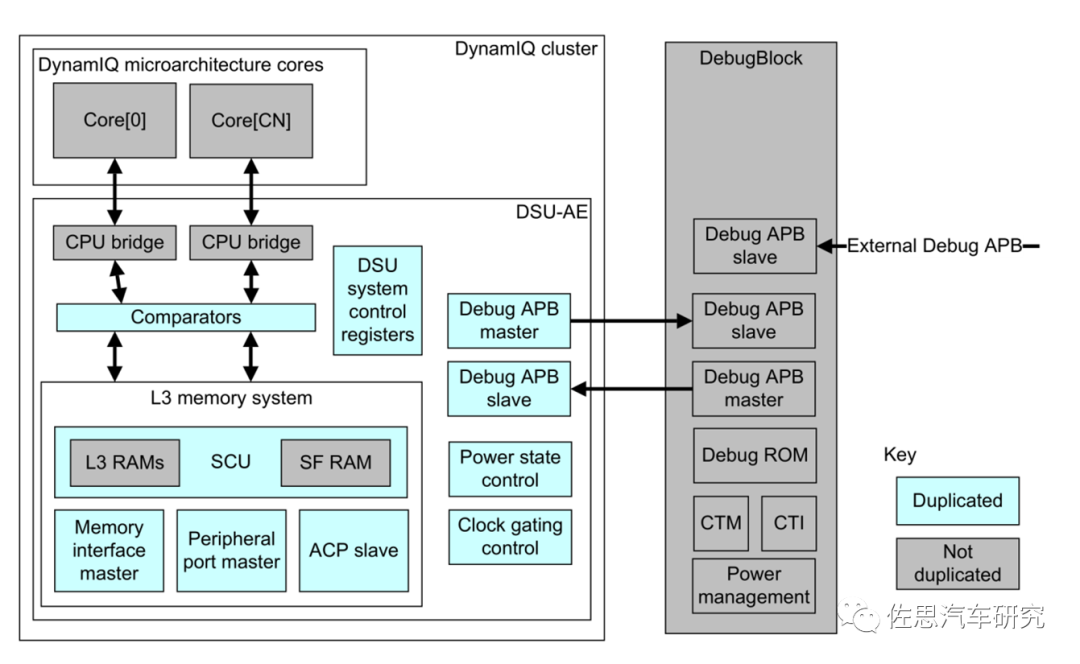

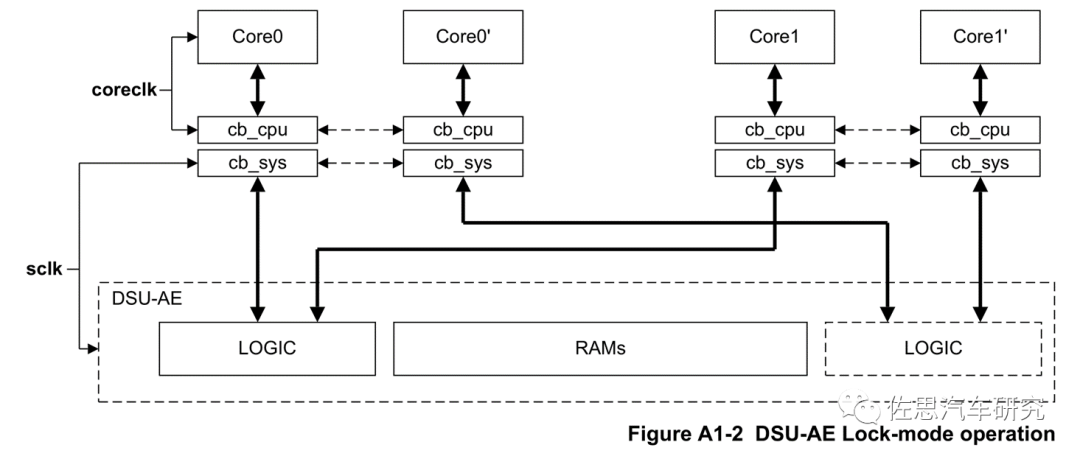

在汽车功能安全标准ISO26262-5 2018产品开发:硬件层面附录D对处理单元的诊断覆盖率推荐的安全技术措施中,作为可实现高诊断覆盖率的几种技术措施之一,硬件冗余技术中,双核锁步、非对称冗余、编码计算是三种典型的技术措施。 锁步是两个核运行同样的程序,将结果输入一个比较逻辑中,周期性比较两个核的输出结果是否相同,即CCM。如果相同,则继续运行;否则,则需采取一定的措施。若一段时间后错误还是存在,可能重启或者重新检查。锁步核的设计是固定在芯片设计中的,所以没有可调整性。容易看出,锁步核虽用了两个核,但其实只起到一个核的作用,浪费了一个核。这种方法已在微控制器和复杂度较低的微处理器领域经过多年的成功验证。如果是设计比较复杂的核,即使未有异常,两个核之间也可能不同步。目前再进一步是将对比结果输出到一个被称为“safety island”安全岛的核中,由这个核负责决策和执行。这个核使用单独的时钟和电源,且有很高的安全性能。这种方案提升了系统复杂度,但软件执行更加灵活。ARM一般推荐是Cortex-R52。 ARM有双重锁步能力,第一重在CPU内部,利用DSU实现,第二重在CPU外部,利用安全岛实现。DSU是DynamIQ Shared Unit ,第一次出现是在A75上。

ARMDSU应用示例

图片来源:互联网

DSU基本构成

图片来源:互联网

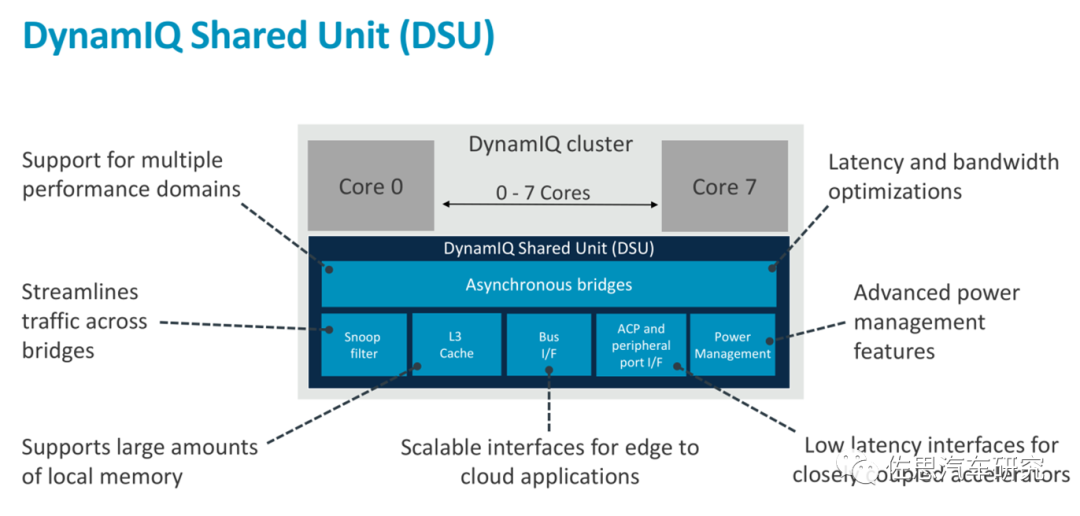

DSU的核心功能是控制CPU内核,使其成簇Cluster使用,簇内每一个核心可以单独开关、调整频率/电压,能效表现更佳,甚至制造商是可以将不同核心(目前仅支持Cortex-A75与Cortex-A55)以不对等的数量放到一个簇内,可以Cortex-A75×3+ Cortex-A55×5,也可以Cortex-A75×1+ Cortex-A55×7,兼顾成本与性能。再有就是L3缓存的共享。DSU能够使用CCI、CCN或是CMN不同总线技术,把CPU与SoC里其它单元(GPU、Modem、内存)高速连接起来;假如它拥有4MB三级缓存,能以动态方式分配缓存给每个核心,比如说Cortex-A75×1+ Cortex-A55×7下,可以将3MB缓存分配给A75核心,剩下7个A55核心共享1MB缓存,甚至可将三级缓存交给GPU等单元使用,灵活性非常高;最重要的是它还负责控制簇内每个CPU核心开关、频率高低、电压大小,是控制CPU性能与功耗的关键。 在设计DynamIQ之时ARM还考虑到冗余需求,比如相比智能手机,汽车对可靠性、冗余度要求高出不少,DynamIQ允许多个簇通过CCIX连接在一起,这样处理器就可以分布于汽车不同位置,当发生交通意外一个簇受损时,DynamIQ技术可以调用出备用处理器,保证汽车正常运转。

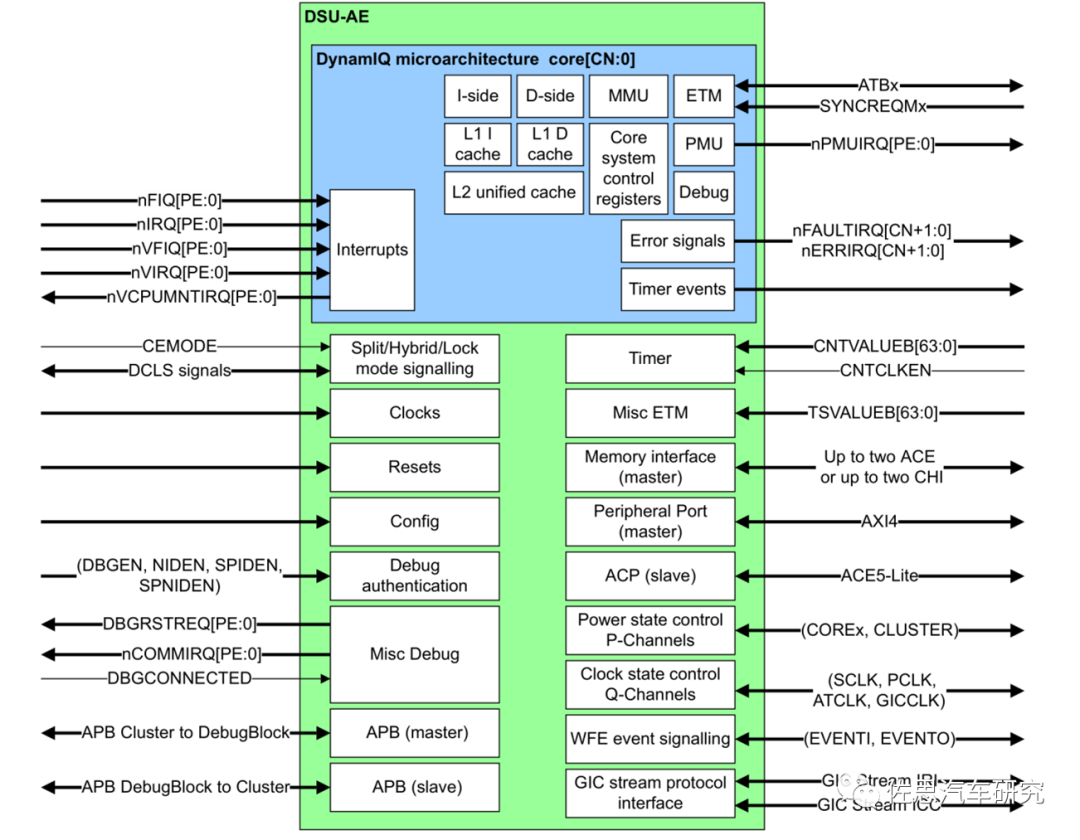

Cortex-A78AE的DSUAE内部框架图

图片来源:互联网

DSU AE主要是添加了比较器,再有就是亮色部分都复制一份,包括执行逻辑、时钟、功率状态,各个界面,当然缓存不能复制,那样成本太高,也意义不大。

DSU-AE锁步模式

图片来源:互联网

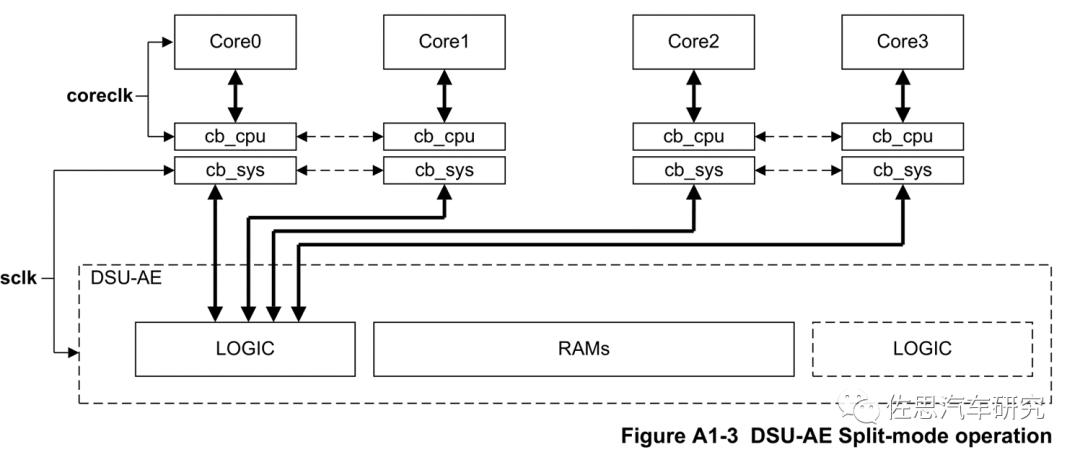

DSU-AE分离模式

图片来源:互联网

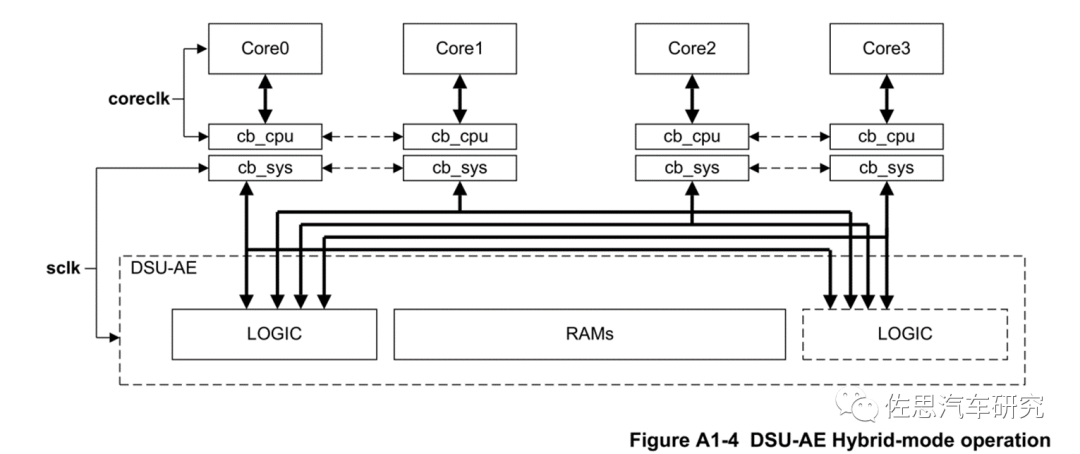

DSU-AE混合模式

图片来源:互联网

DSU-AE界面

图片来源:互联网

除了DSU还有针对汽车功能安全的GPU架构G78AE,图像ISP的C71AE,中断控制GIC-600AE,存储管理MMU-600AE,网格总线CMN-600AE。但DSU最关键。

二、ARM的片上总线

ARM智能驾驶产品全系列

图片来源:互联网

数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线是连接各模块,对各模块做出仲裁的核心系统,是设计最关键的问题。AMBA总线是ARM研发的(Advanced Microcontroller Bus Architecture)提供的一种特殊的机制,可将RISC处理器集成在其他IP芯核和外设中,是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件。它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。AMBA规范主要包括了AHB (Advanced High PerformanceBus)系统总线和APB (Advanced Peripheral Bus)外围总线。除了AMBA总线,ARM还有应对多核的GIC中断控制,MMC内存控制。

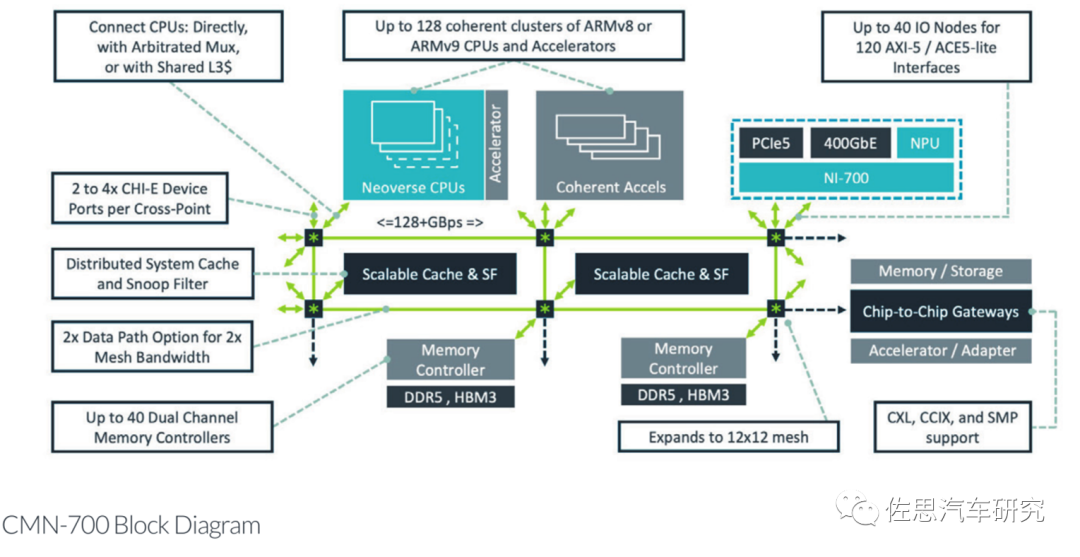

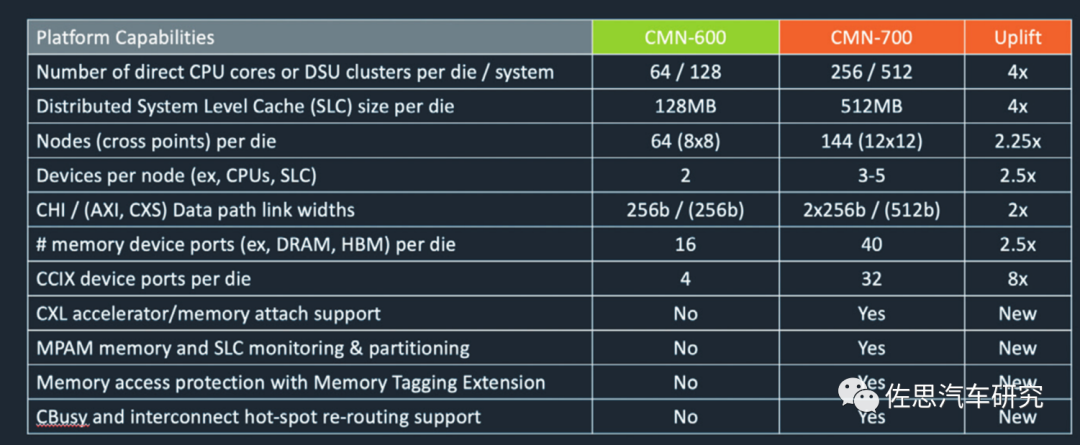

ARM CMN-700

图片来源:互联网

ARM发展了一种介于总线和NoC之间的连接系统,称之为CMN,主要用于连接CPU内核,也可以CPU内核和加速器之间的连接。采用MESH网格结构,但没有路由功能,本质上还是总线,但MESH网格支持的单元很多,远比一般总线要多,最高可支持512核,支持512MB的L3缓存,目标市场主要是HPC领域。

CMN-700同时还支持AMBA AXI5、ACE5-lite、CXS和CCIX

附录:ARM架构一览

- 下一篇:CANoe集成解决方案

- 上一篇:电池容量和寿命

编辑推荐

最新资讯

-

标准解读丨ISO 21111 《道路车辆车载以太网

2025-03-31 19:15

-

清研精准兆瓦级充放电测试设备——重新定义

2025-03-31 19:13

-

强强联合:imc FAMOS内嵌Python接口,提高

2025-03-31 19:12

-

汽车动力电池与发动机系列标准宣贯会在武汉

2025-03-31 16:08

-

氢内燃机2.0-西南研究院(SwRI)启动第二阶

2025-03-31 16:06

广告

广告