车规MCU的eFlash原理

目录

1.Flash基本原理概述

1.1 Non-volatile Memory的分类

1.2 Flash编程\擦除原理

1.3 NOR\NAND Flash

2.eFlash在先进制程中的挑战

3.小结

1. Flash基本原理概述

1.1 Non-volatile Memory的分类

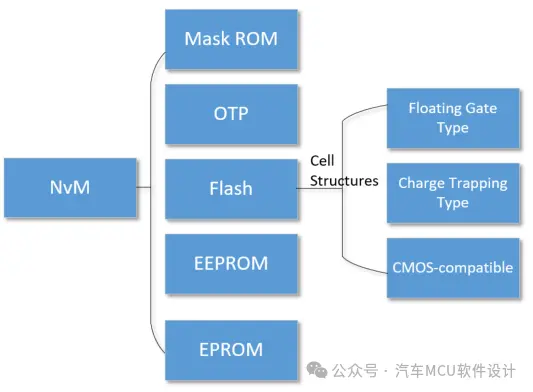

Flash在嵌入式领域是非常重要的角色,主要用于存储数据代码,为代码的执行提供基础保证等。实际上,Flash只是Non-volatile Memory中的一个分支,根据《Embedded Flash Memory for Embedded Systems》整理,嵌入式领域的非易失性存储器分为ROM、EEPROM、Flash等,如下图所示:

- Mask ROM是在芯片掩膜阶段写入数据或者代码,对于MCU来说最常见就是启动代码,例如英飞凌的BootRom,一旦写入,用户就无法进行修改;

- OTP类似Mask ROM,可以由用户写入敏感数据等,例如密钥、设备独有信息等;

- EPROM(Electrically Programmable ROM):按字节编程,但不能擦除;

- EEPROM(Electrically Erasable and Programmable ROM):按字节擦写,成本较高;

- Flash则是软件开发人员最常接触到的存储器之一,它根据存储单元的结构分为浮栅型、电子捕获型等。

1.2 Flash编程\擦除原理

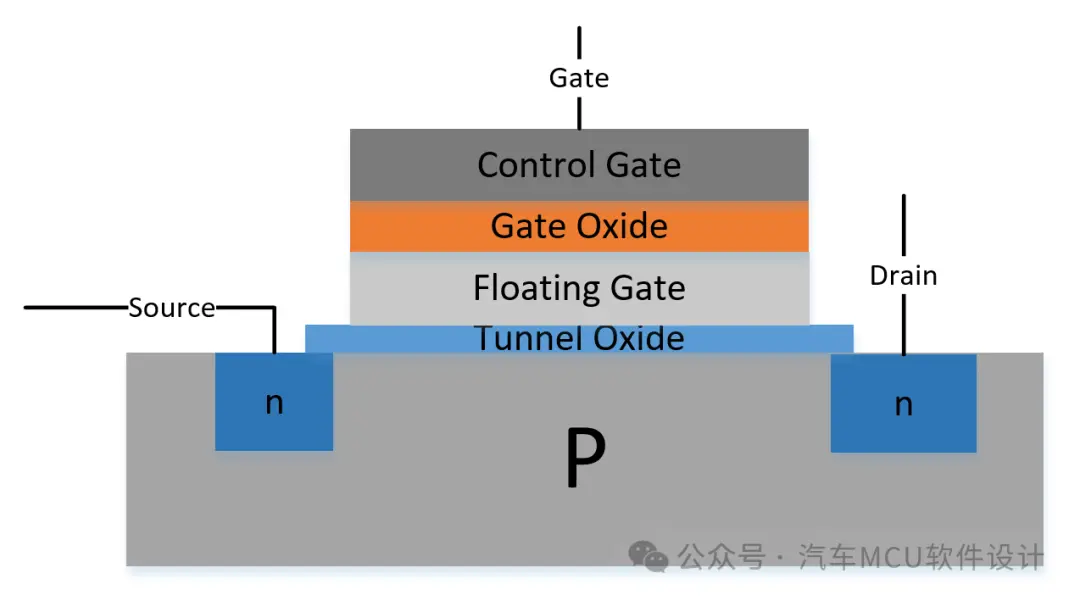

以浮栅型Flash为例,它基本存储单位为bit,其存储物理结构叫做cell,这个Cell其实就是一个带浮栅的MOSFET,如下所示:

可以看到,浮栅晶体管在控制栅极(CG)下的绝缘层(Gate Oxide)新增了一层浮栅极(FG),用于保存电子。

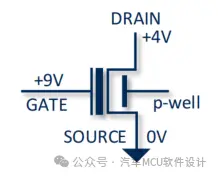

一般情况下,源极和漏极里有电子,但是因为它们之间有缺电子的P型材料,因此没法流通。如果此时我们给CG和漏极施加正电压,源极接地,如下图:

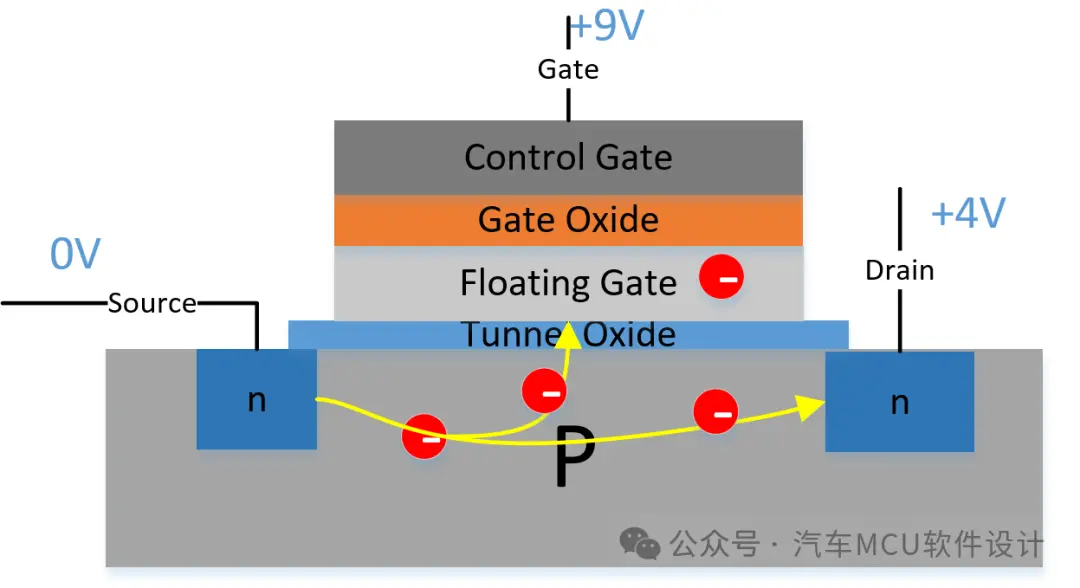

电子就会迅速从源极流向漏极,同时由于CG电压更大,一部分电子通过隧穿效应(Quantum Tunneling Effect)通过隧道氧化层进入到FG,如下图:

这种情况下即使正电压被移除,电子也会因为隧道氧化层的绝缘作用保存在FG里,这种状态我们说晶体管存储了一个0,表示被编程了。

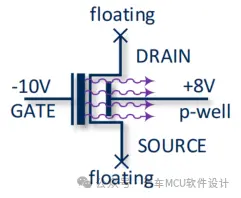

当我们想要擦除的时候,则在CG施加反向电压,如下:

在这种状态下,电子会被排斥并通过隧道氧化层回到P-Well中,这种状态对应“1”,即擦除状态。

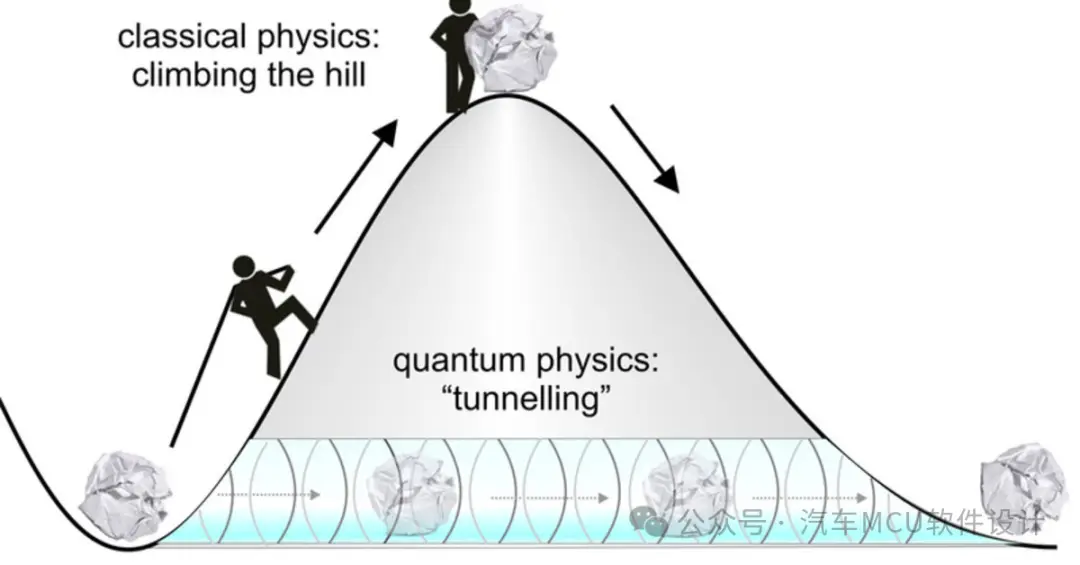

这里我们提高了隧穿效应,所谓量子隧穿效应,即很多粒子冲向势垒,一部分粒子反弹,还会有一些粒子能通过一个隧道穿过势垒,如下图,这个隧道称作“量子隧道(quantum tunneling)”。

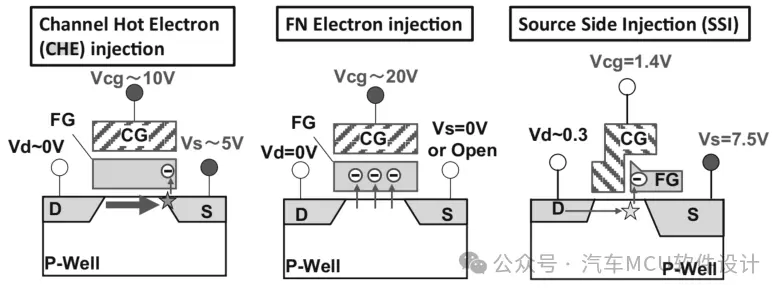

实际上,针对浮栅型Cell的Flash来说,编程常用CHE、FN、SSI等三种方式进行操作,如下图:

- CHE:通过对CG和源施加高的电压,电子在源侧经过水平高电场加速,通过垂直高电场注入到FG,这种情况编程电流相对大;

- FN:隧穿效应,如上所示;

- SSI:该方式需要在源极施加高电压,CF和漏极电压较低,从而容易在FG和CG之间的间隙区域诱导出更高的电场。由于水平电场和垂直电场在间隙区都具有最大的场强,因此在间隙区可以高效率地产生热电子并注入到FG中。

1.3 NOR\NAND Flash

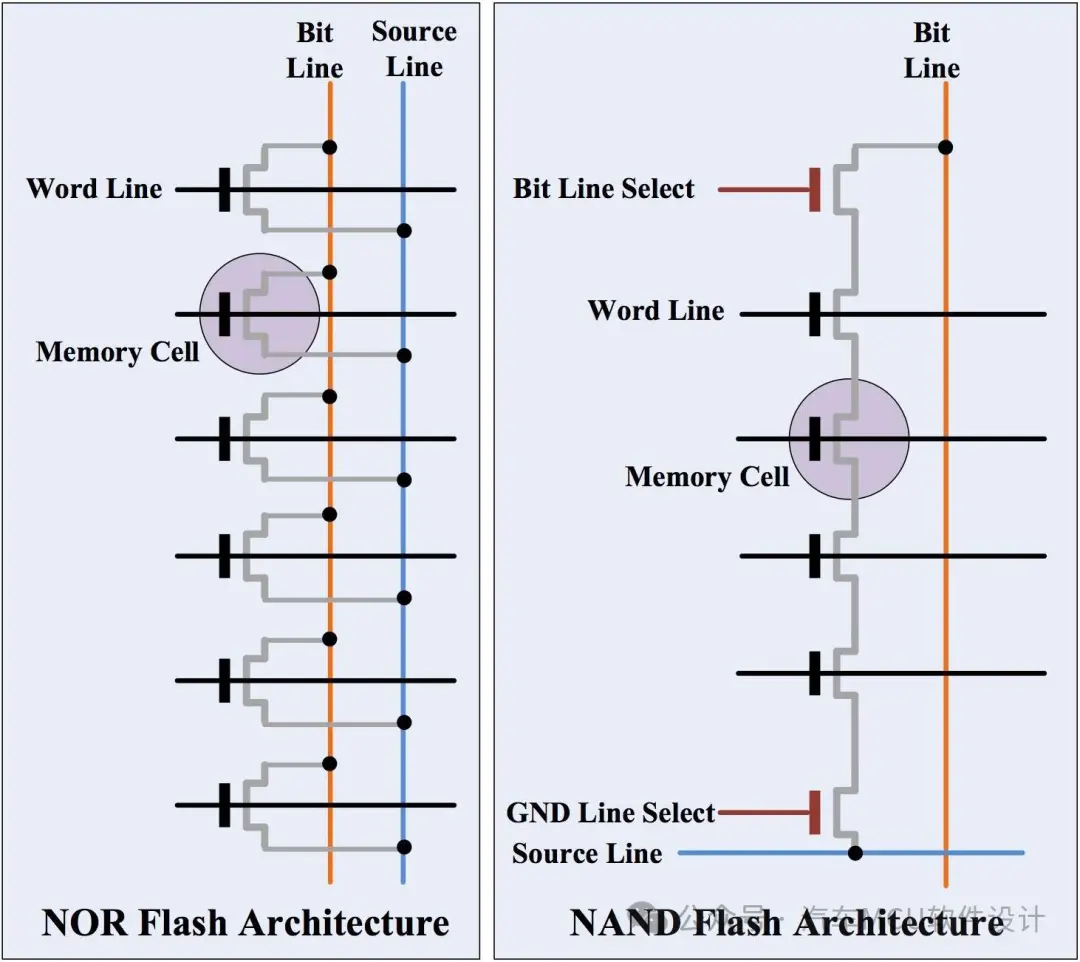

在了解了Flash Cell的基本原理后,我们来看看目前市面上常见的存储器类型。按照架构分为两类:NOR(或非) Flash和NAND(与非) Flash,具体如下。

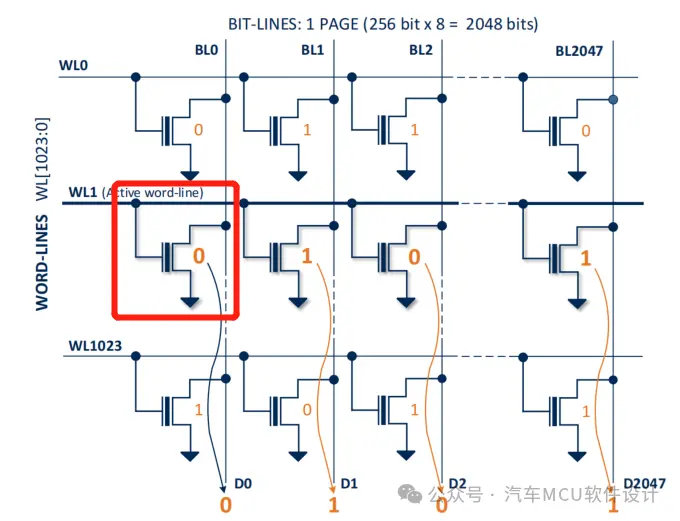

我们把1.2节里的CG、Drain和Source分别对应WL(Worl Line)、BL(Bit Line)和SL(Source Line),可以明显发现NOR Flash中每个Cell均为并行连接,只要有一个WL拉高,对应的BL就会拉低,因此叫做NOR;

NAND Flash则把所有Cell串联起来,必须所有的WL 拉高,BL才会拉低,因此叫做NAND。

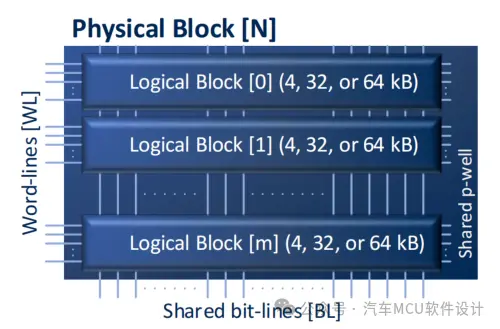

通常根据厂家不同,WL下挂的所有Cell组成一个Page,多个WL组成一个logic Block(也叫logic sector),多个logic sector组成一个物理Block(也叫Bank)。如下:

可以看到,在Flash读的效率上,由于NOR Flash的并行连接,因此具备更好的随机访问能力(可以快速读某个bit),而NAND Flash的访问必须要先读取Page,效率较低。

在擦写操作上,NOR Flash擦除只能在块的基础上执行,而写过程可以每次在单个字节或单字上执行,而NAND Flash要求在写入新数据之前先以块的形式擦除数据。

因此,我们可以发现NOR Flash和NAND Flash经常应用在不同场景:

- NOR Flash:MCU代码存储和执行,需要高速随机访问能力;

- NAND Flash:适合大容量存储,代码需要拷贝至RAM运行。

事实上,我们上述仅仅讨论的是浮栅型技术路线。AMD、东芝、三星一直致力于电荷捕获型(Charge Trap)技术路线。这里没有具体研究,就不谈了。

2. eFlash在先进制程中的挑战

车规MCU的eFlash由于需要存放和执行代码,因此通常均为NOR Flash架构;

随着车规MCU的性能要求越来越高,大厂开始尝试使用先进制程,但在推进的过程中,可以很容易定位到Flash的稳定性与工艺之间有一个比较大的矛盾。

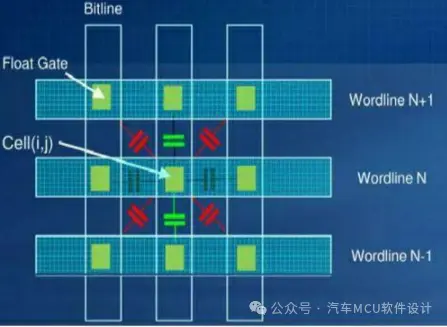

我们知道,NOR Flash是由WL和BL交织组成,每个交织点表示一个Cell存放电子。如下:

存放电子的实体是浮栅,它与P-Well之间的隧道氧化层是保证电子不出现逃逸的重要组成,一旦制程变小,该绝缘层相应就会变得更小,这就更容易出现电子逃逸的情况,这是eFlash往先进制程迈进的桎梏之一;

其次,随着制程的缩小,cell之间的距离也越来越近,两个相近的绝缘体之间构成电容,所以一个存储单元Cell会与周边Cell形成耦合电容,这就会影响其他Cell的电荷大小,会导致存储单元“写不准”、“读不准”,因为我们不知道一个存储单元的Vt中,究竟有多少成分是隶属于周边浮栅的耦合效应,又有多少是存储单元真实的Vt,这样也就更容易出现Flash位翻转问题。

最后回到制程缩小导致的浮栅尺寸缩小,那自然保持电荷的能力也会进一步下降;

此外如何考虑功耗、散热以及最重要的成本问题,目前也没有看到比较成熟的eFlash先进制程解决方案。

3. 小结

本文主要分析了Flash的分类,利用易于理解的隧穿效应来解释了Flash的基本原理。

事实上,随着eFlash逐渐逼近物理极限,我们可以看到各大MCU厂商正在寻找其他的存储解决方案,例如PCM(Phase-Change Memory):相变存储器、STT-MRAM(Spin-Transfer Torque ):嵌入式自旋转移矩磁阻RAM、RRAM(Resistive RAM):电阻随机存储器。

而eFlash是否会退出历史舞台?我们拭目以待!

编辑推荐

最新资讯

-

自动驾驶卡车创企Kodiak 将通过SPAC方式上

2025-04-19 20:36

-

编队行驶卡车仍在奔跑

2025-04-19 20:29

-

全国汽车标准化技术委员会汽车节能分技术委

2025-04-18 17:34

-

我国联合牵头由DC/DC变换器供电的低压电气

2025-04-18 17:33

-

中国汽研牵头的首个ITU-T国际标准正式立项

2025-04-18 17:32

广告

广告