MOSFET器件的高压CV测试详解

介绍

MOSFET、IGBT和BJT等半导体器件的开关速度受到元件本身的电容的影响。为了满足电路的效率,设计者需要知道这些参数。例如,设计一个高效的开关电源将要求设计者知道设备的电容,因为这将影响开关速度,从而影响效率。这些信息通常在MOSFET的指标说明书中提供。

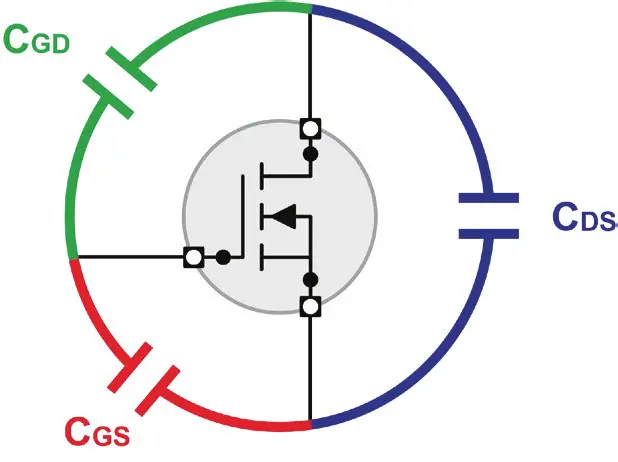

三端功率半导体器件的电容可以在两种不同的量级上看待:组件和电路。在组件上查看电容涉及到表征每个设备终端之间的电容。在电路上观察电容涉及到描述组件级电容的组合。例如,图1说明了一个功率MOSFET的组件级电容。

图1. 功率MOSFET的组件级电容

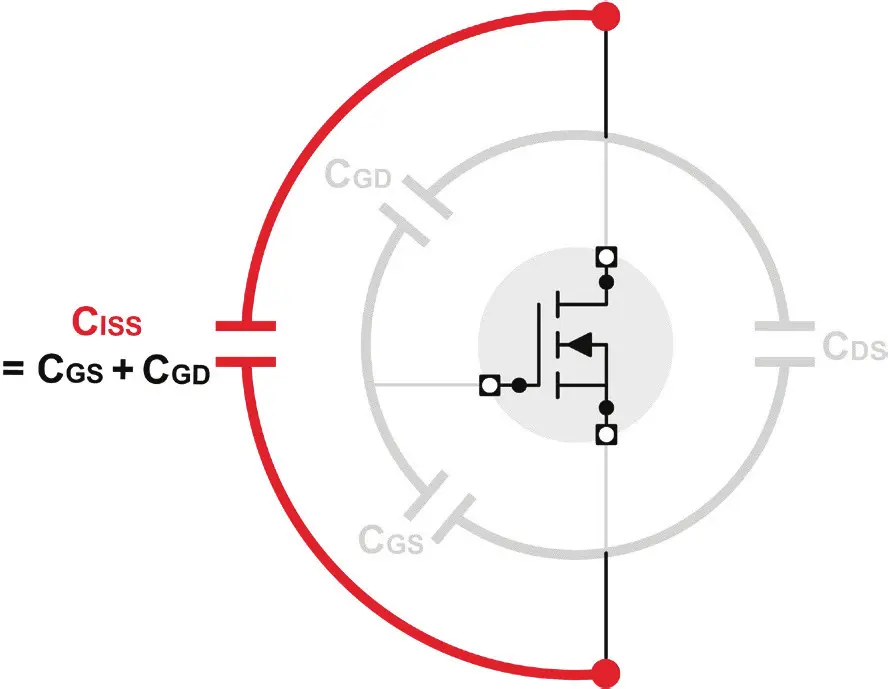

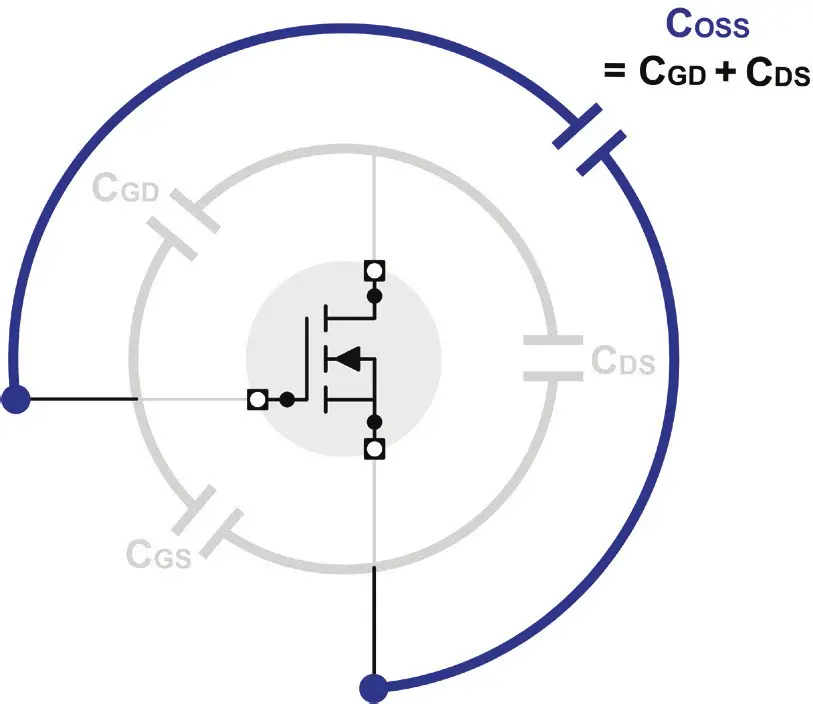

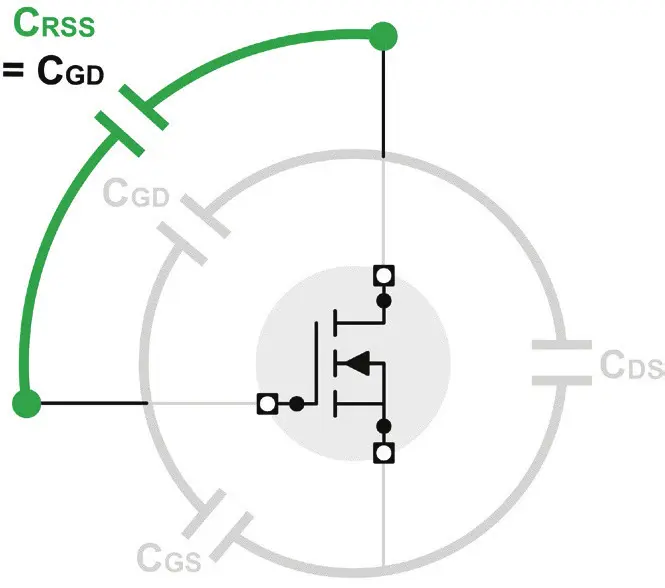

图2到图4说明了一个功率MOSFET的组件级和电路级电容之间的关系。对BJT和IGBT器件也可以进行类似的电容测量。

关系如下:

•CISS = CGS + CGD = 输入电容

•COSS = CDS + CGS = 输出电容

•CRSS = CGD = 反向传输电容

图2. 功率MOSFET的输入电容

图3. 功率MOSFET的输出电容

图4. 功率MOSFET的反向传输电容

器件的电容通常随所施加的电压而变化。因此,完整的表征需要了解在最大额定电压下的电容。本应用程序说明了如何使用4200A-CVIV开关提供的偏置功能以及在Clarius中测量CISS 、COSS和CRSS的。CVIV可以很容易地在I-V和C-V测量值之间切换,它还可以将C-V测量值移动到任何设备终端,而无需重新连接或抬起探针。

本应用文档还显示了仪器的直流输出电压如何从200V 加到400V,进行漏极上更高电压的测量,这有利于测试更高功率的半导体,如GaN器件。该功能已在Clarius V1.6以上的版本添加并更新。本应用文档的前提是熟悉使用4200A-CVIV使用Keithley4200A-SCS进行C-V测量。

设备连接

本应用文档中描述的所有SMU和CVU连接都是通过4200A-CVIV进行连接的。CVIV可以有一个4210-CVU或4215-CVU,最多可以有四个SMU连接到一个设备上。有关更多信息,请参阅4200A-CVIV多开关用户手册。

使用4200A-CVIV提供了以下优点:

•内置都项目可测量高达200V和400V的CISS、 CRSS和COSS。

•4200A-CVIV开关支持自动测量。不需要重新连接设备或电缆。

•开路和短路的C-V补偿。

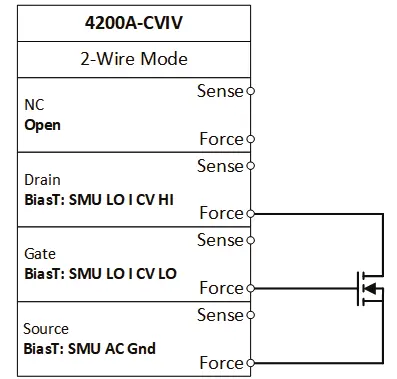

图5显示了MOSFET与CVIV的连接。对于这个特定的应用程序,至少需要三个smu和一个CVU来完成测试。

图5. MOSFET连接到4200A-CVIV的输出端

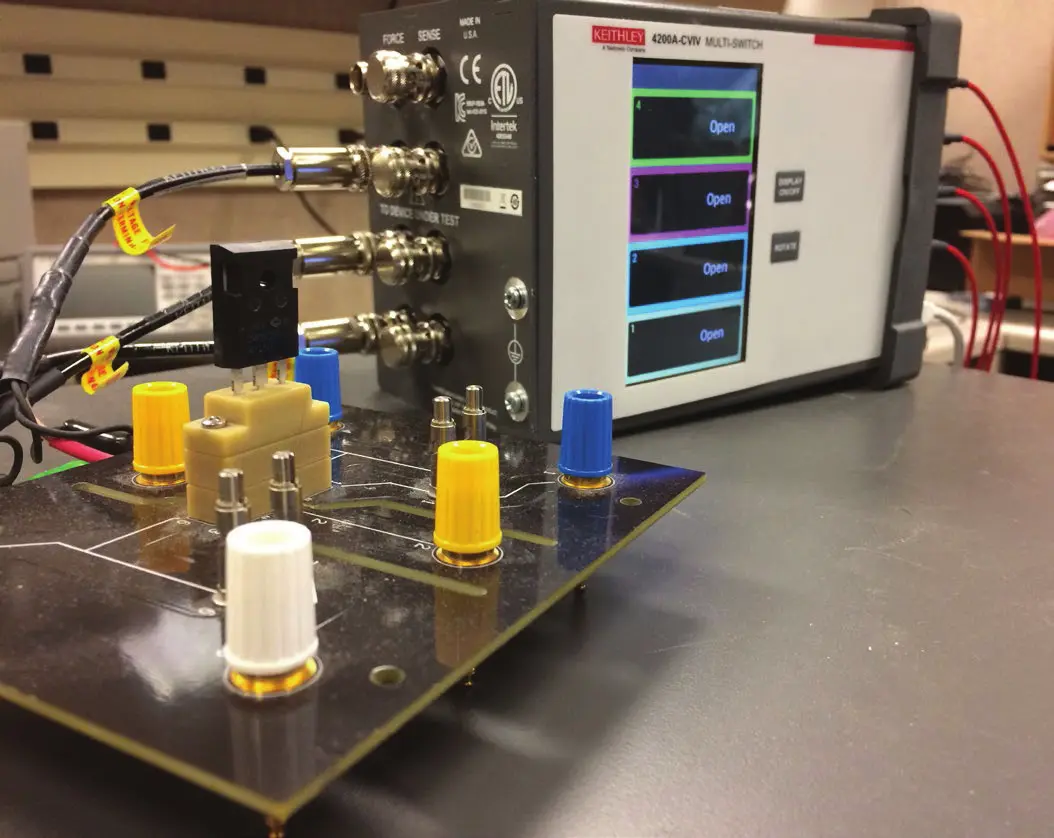

图6显示了封装的MOSFET的实际CVIV连接。请注意,CVIV 上的所有通道都是打开的。4200A-CVIV 的四个通道将根据每次测试的配置进行配置,因此每次测试都不需要电缆重新连接。

图6. 连接到4200A-CVIV的封装MOSFET

在Clarius软件中配置测量

Clarius的库有两个在mosfet上执行三端电容测量的项目。这两个项目在 Clarius 中配置相似,不同之处在于能力。一个项目,“MOSFET 3-terminal C-V Test Using 4200A-CVIV Bias Tees”使用一个SMU加到漏端,从0到200V直流偏置电压扫描。另一个项目,“MOSFET 3-terminal C-V tests up to 400 V using 4200A-CVIV Bias Tees”使用一种新方法将电压从0到400V。这种方法同时使用三个SMU扫描,每个器件端口上一个SMU,提供一个400V直流差分电压。

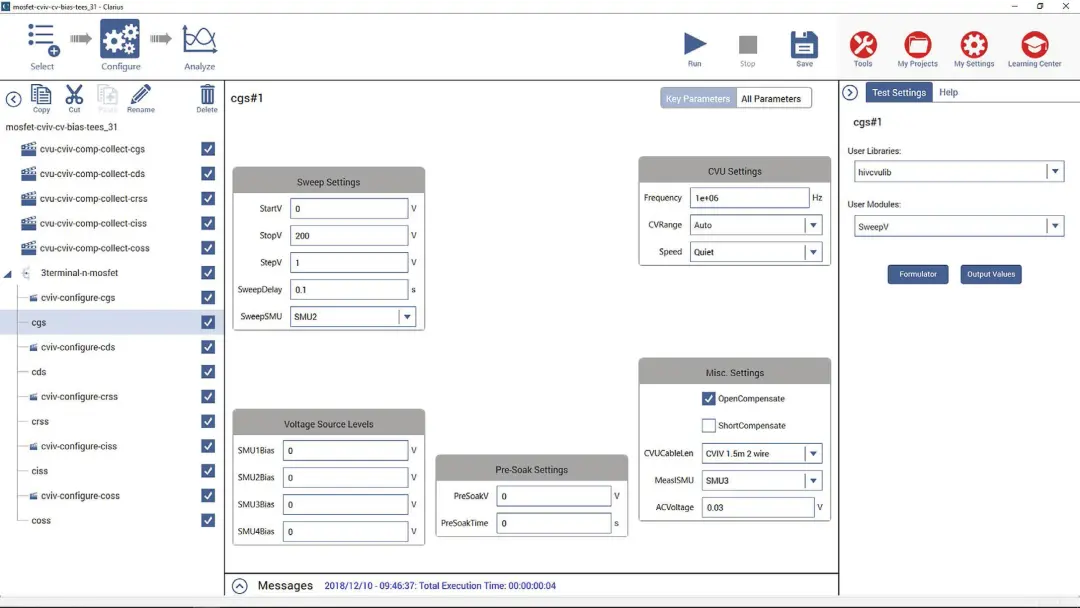

图7. 使用SweepV用户模块的MOSFET-CVIV-CV-Bias-Tees项目

图7显示了“使用4200A-CVIV BiasT的MOSFET3端C-V测试”项目,该项目使用了hivcvulib中的SweepV用户模块。

该用户模块允许在漏极处进行一次扫描,并在器件每个端口处进行电容测量。

首先,进行开路和短路补偿,以确保准确的测量。执行这些补偿需要执行特定的配置步骤。它们被称为补偿测量,并在项目树中提供。在执行任何测试之前,将对每个测试执行补偿。4200A可以存储对每个配置的补偿,可以执行多个测试。

该项目有五种不同的配置:CISS、CRSS、COSS、CGS和CDS 。

CVIV配置

必须为每个测试配置CVIV。CVIV有许多输出模式,这些都在用户手册中有描述。表1列出了各种输出模式。

表1. 4200A-CVIV输出模式

|

4200A-CVIV输出模式 |

应用程序和描述 |

|

开路 |

默认设置。还断开与设备的通道 |

|

SMU |

用于I-V测量。连接Force Hi和Sense Hi到器件。 |

|

CV Hi |

用于C-V测量。将CVU(HPOT和HCUR)连接到该设备。 |

|

CV LO |

用于C-V测量。将CVU(LPOT和 LCUR)连接到该设备。 |

|

CV Guard |

用于在多终端设备上进行C-V测量时保护不必要的阻抗。对排除C-V测量的器件应用CV保护。 |

|

Ground Unit |

用于I-V测量。将Force LO和Sense LO连接到器件。 |

|

AC耦合到AC地 |

用于C-V测量。允许交流路径到地面,而不提供直流路径。 |

|

BiasT SMU CV HI and BiasT SMU CV LO |

用于高达200V直流偏置的C-V测量。允许高达1A的直流电流,理想的状态设备测量。 |

|

BiasT SMU LO I CV HI and BiasT SMU LO I CV LO |

用于高达200V的DC偏置测量。允许高达100µA的直流电流,理想的关态设备测量。 |

|

BiasT SMU AC Gnd |

用于在多器件设备上进行C-V测量时保护不必要的阻抗。允许直流偏置高达200V。应用BiasT SMU AC Gnd的器件被排除在C-V测量之外。 |

图8到图12显示了对每个元件和电路级电容测量的CVIV的每个通道的状态。

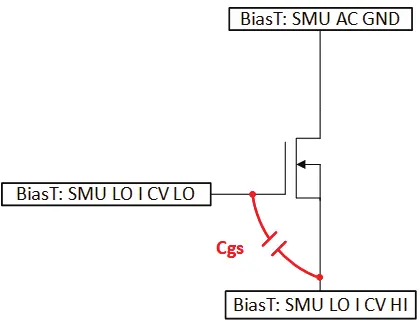

图8. CGS配置

图8显示了CGS的配置。当SMU在漏极处扫描直流电压时,该测试测量了MOSFET的栅极和源极之间的电容。

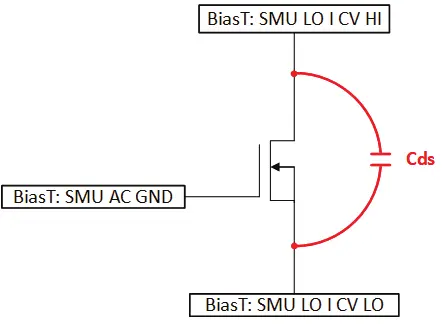

图9. CDS配置

图9显示了CDS的配置。当SMU在漏极处扫描直流电压时,该测试测量了漏极和源极之间的电容。

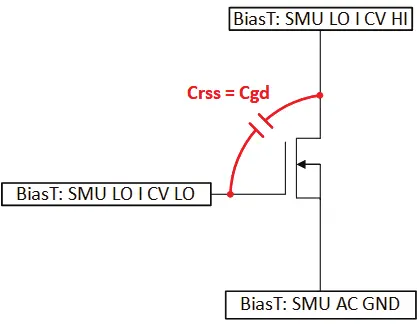

图10. CRSS和CGD配置

图10显示了CRSS配置。该测试测量MSMU扫扫漏极直流电压时MOSFET的反向传输电容。

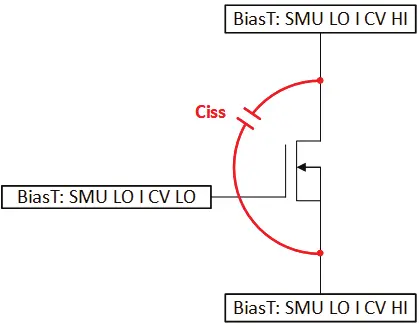

图11. CISS配置

图11显示了CISS的配置。该测试测量MSU扫描直流电压时,MOSFET的输入电容。

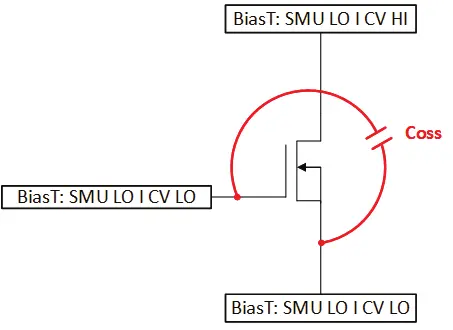

图12. Coss配置

图12显示了COSS配置。该测试在SMU扫描漏极的直流电压时测量MOSFET的输出电容。

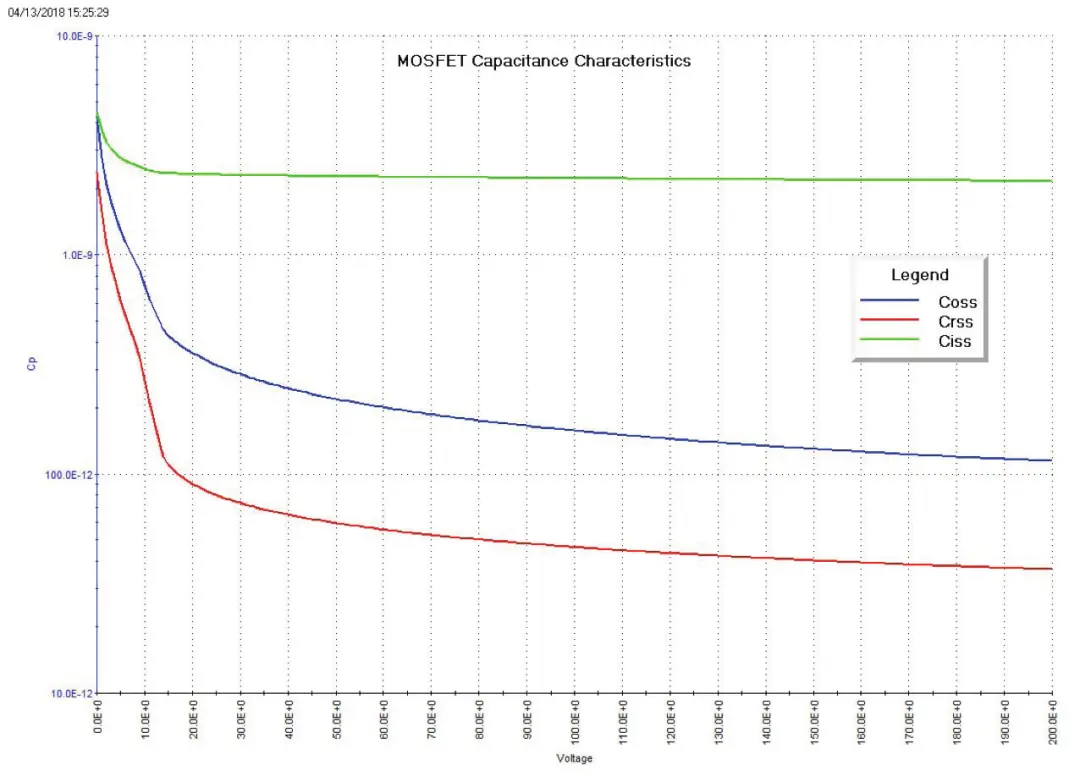

一旦执行了测试,数据就会被绘制出来。图13显示了由4200A生成的MOSFET的电容特性数据。

图13. MOSFET扫描到200V的电容特性

400V直流电压扫描

利用4200A-CVIV多开关同时扫描多个SMU,将MOSFET器件的输出电压翻倍至400V的新方法。这些测试通常在OFF状态(VGS = 0V)下进行。通常在漏极有一个扫描SMU,使用4200A-CVIV内置的偏置能力,在每个终端测量电容。

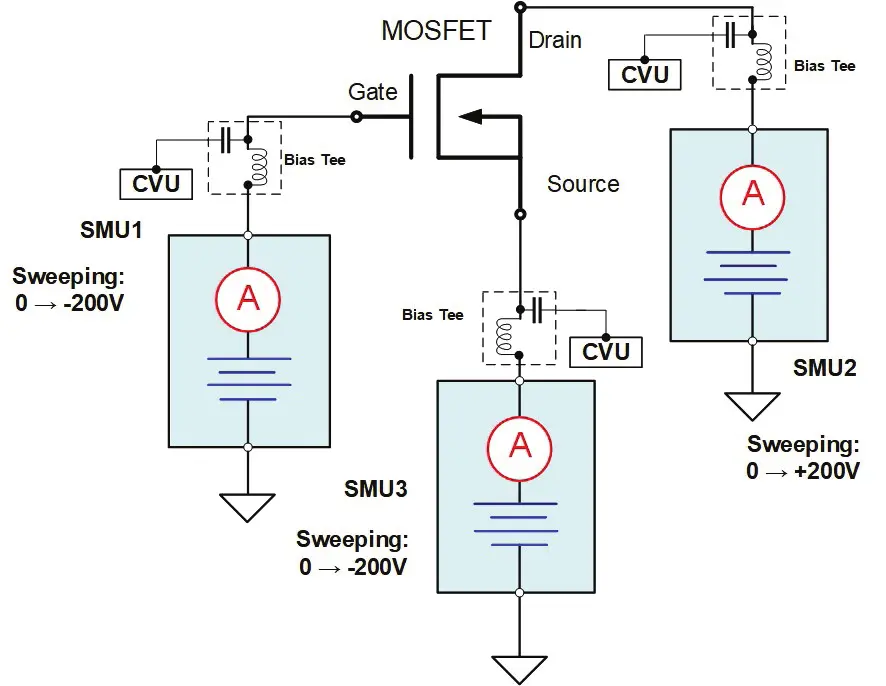

图14. 三个SMU同时扫描

图14显示了连接到MOSFET的三个端口的三个扫描SMU。SMU1和SMU2将使用高达400V的差分电压。SMU2和SMU3必须在相同的电压下同时扫描,这可以使栅极下降0V。使用这种方法,我们可以在Drain端产生一个400V的扫描电压。

注:此方法仅用于封装器件,而不适用于晶圆级设备。

这些测量是使用multiple SMU_SweepV用户模块执行的,可在hivcvulib用户库中获得。

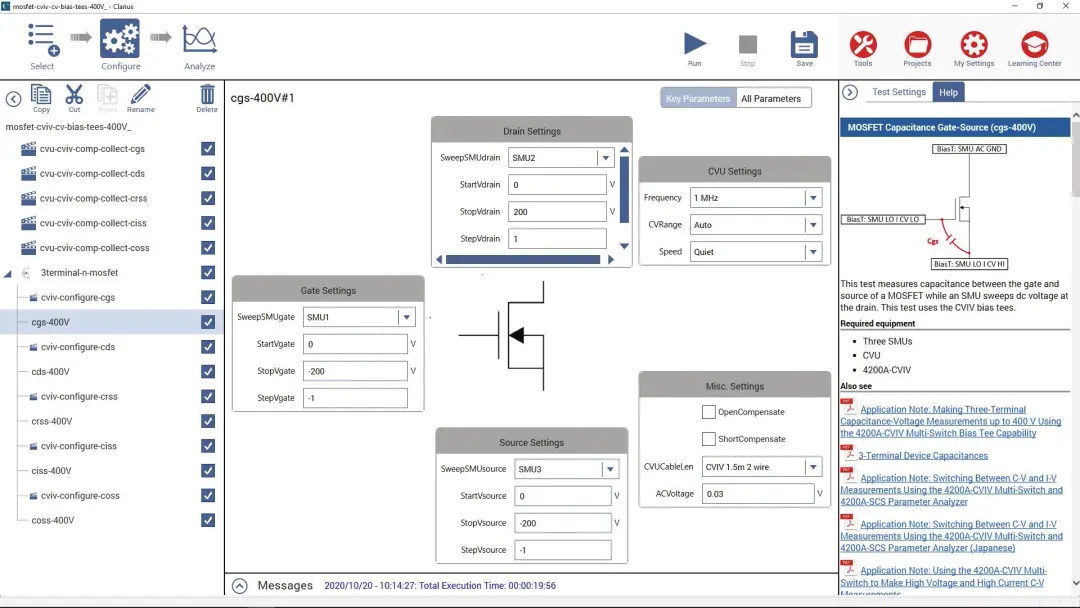

图15. 输出高达400V直流差分的项目

图 15 显示了使用用户模块MultipleSMU_SweepV的4200A-CVIV Bias Tee项目进行高达400V的MOSFET三端口C-V测试

项目树的设置方式与上一个项目相同。所有的CVIV配置操作,包括补偿,都以完全相同的方式完成。唯一的区别是,还必须配置另外两个SMU。

默认情况下,测试应该在Drain上从0扫到400V。栅极和源极SMU应同时在相同的电压下扫描。

用户还能够根据被测试设备的阻抗来改变CVU设置,如频率、范围和速度。

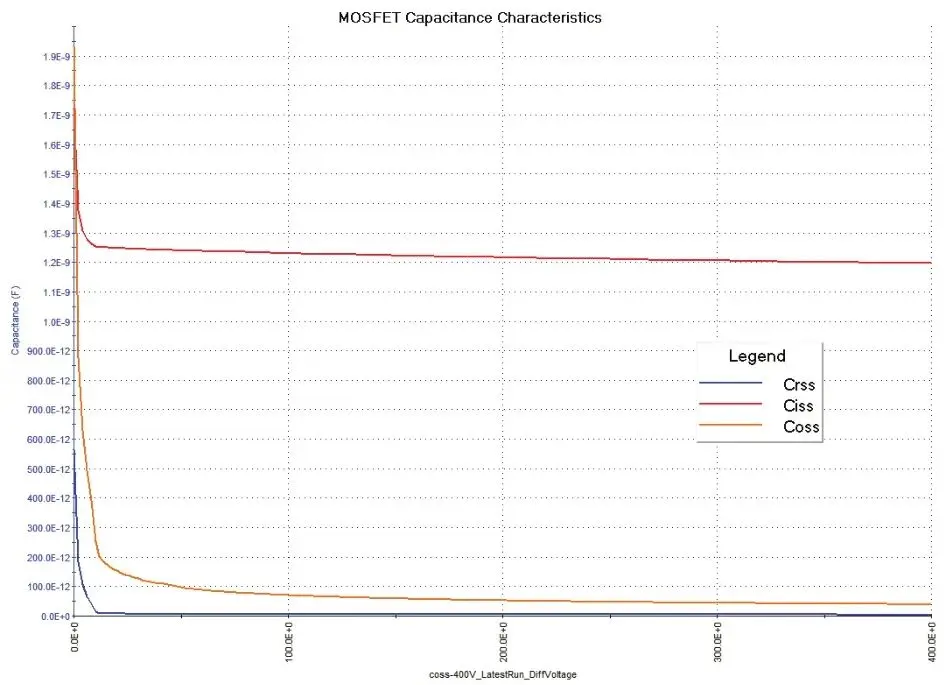

图16. MOSFET扫描到400V的电容特性

图16显示了由4200A-SCS中测试MOSFET上高达400V的C-V扫描图。差分电压为一个计算值。区别在于漏极和源极之间的电压不同。

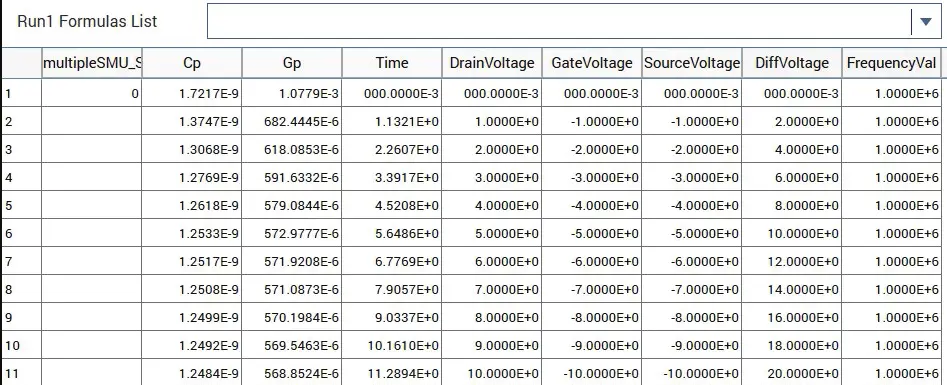

图17. 400V扫描的输出数据

图17显示了输出数据,其中列出了三个端口上的扫描电压。Diffvoltage是计算出的差分电压值。

总结

MOSFET、IGBT和BJT等半导体器件的开关速度受到元件本身电容的影响。本应用程序说明了如何使用4200A-CVIV能够在不需要重新连接任何电缆的情况下,在200V直流偏置的情况下进行这些测量,从而减少了用户错误并允许自动测试。它还允许直接测量电路级电容,而不需要通过组件级电容,这允许电路级设计者更快地获得所需的数据。

此外,当在三端器件上测量电容时,通常有一个端子不包括在测量中,其电容可能会影响整体测量。在每个端口使用偏置网络消除了外部电容或短路的影响。

我们还展示了一种新的方法,通过同时使用三台smu进行扫频,使在三端器件上的4200A的直流偏置加倍。栅极和源极SMU在同一极性上同时扫描,以避免设备的开态状态的影响。漏极SMU将扫描源极和栅极的相反极性,从而使差分电压翻倍。这支持在漏极处进行高达400V的电压扫描,这有利于测试更高功率的半导体,如GaN。

最新资讯

-

风噪测试在电动汽车时代的关键作用

2025-04-29 11:34

-

汉航车辆性能测试系列之操纵稳定性测试--汉

2025-04-29 11:09

-

新能源汽车热管理系统验证体系PITMS正式发

2025-04-29 11:09

-

试验载荷谱采集

2025-04-29 11:07

-

APx500 软件演示模式 (Demo Mode) 竟有这些

2025-04-29 08:37

广告

广告