芯科技 • 2024年度总结

作者:赵传猛,阳任平

2024年,对半导体人来说,注定是不平凡的一年,我们一起见证和经历了半导体产业的复苏和算力大爆发。

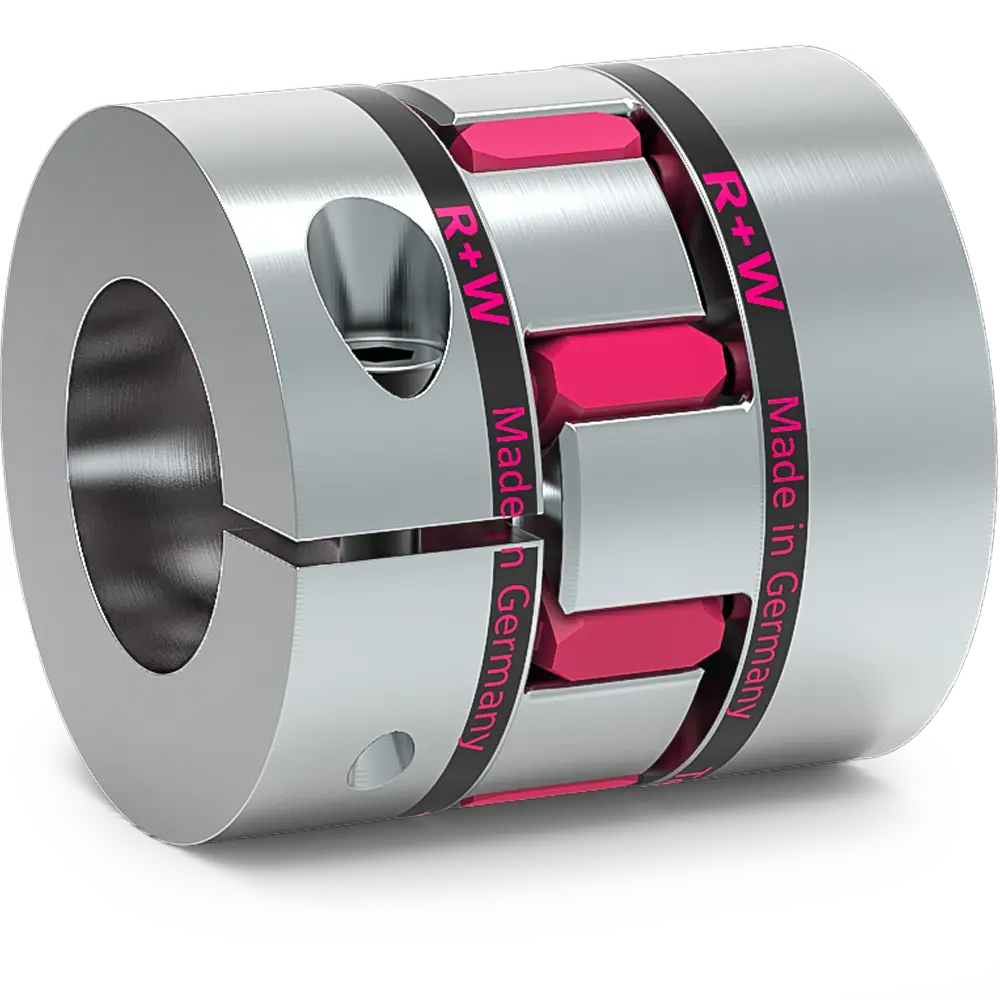

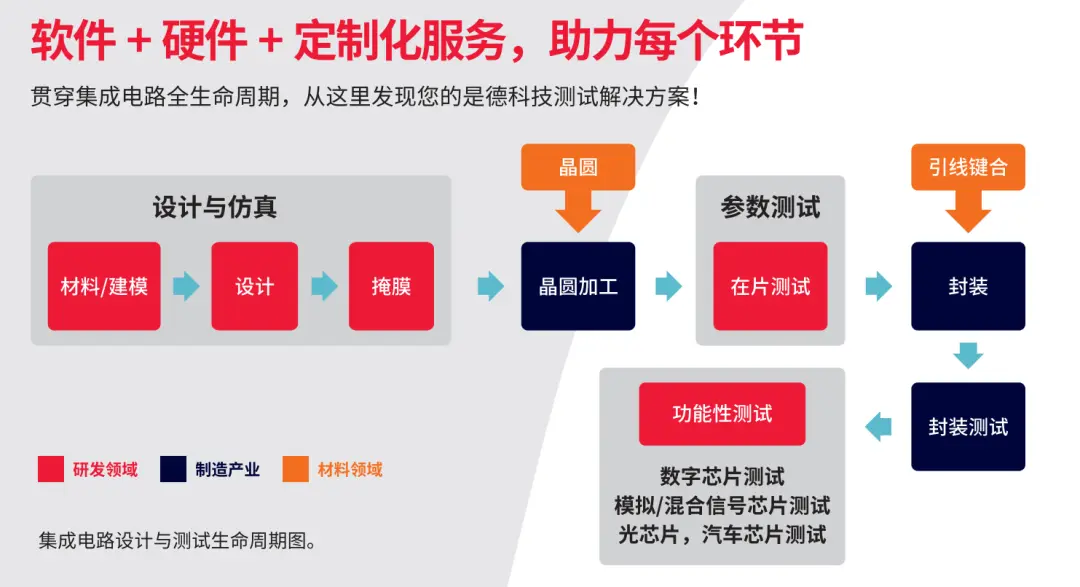

是德科技在半导体产业链中的价值

图:是德科技在半导体产业链中的价值

半导体产业链是一个复杂且高度专业的全球网络,Keysight有幸参与其中。半导体从开始设计到最终用户中间经历产品设计、前道工艺、后道工艺及板级组装环节。产品(比如芯片)设计阶段需要硅前仿真,Fab厂完成前道工艺会进行工艺评估、CP测试、FT测试、WAT测试,封测厂完成后道工艺会进行晶圆封装后的测试,最终设计厂商拿到芯片会进行bring up、一致性测试等。环环相扣,是德科技提供了硬件 + 软件 + 定制化服务的完整解决方案。

01、芯片设计阶段,Keysight 的Pathwave ADS软件是模拟芯片尤其是RFIC或者MMIC的重要工具,同时也在电磁仿真、信号完整性仿真、电源完整性仿真、热仿真等方面发挥重要的作用。

02、前道的工艺评估阶段Keysight跟很多的Foundry和IDM厂商有合作,提供从DC到高达120GHz的器件建模解决方案,这其中包含建模所需要的测量工具如IV/C-V/脉冲&动态半导体参数表征与分析设备B1500A,Vth/Ids/Idoff/Cox等直流&电容基本参数串行测试设备4080B,逐引脚并行参数测试设备P9000A等 , 用于功率器件分析的B1505A,用于低频闪烁噪声/随机电报噪声分析的噪声分析仪E4727B、用于射频测量的PNA网络分析仪,包含建模所需的软件MBP, IC-CAP等,以及建模验证的软件MQA等。被国内外的IDM、foundry、以及一些建模相关的高校、研究所等广泛使用。

03、前道的测试阶段包含晶圆CP测试、WAT测试。CP测试的测试对象是整片Wafer中的每个Die,通过测试确保每个Die满足设计规格书,通常测试直流特性,B1500A是常用设备。WAT测试是晶圆流片之后、品质检测之前Fab厂出厂前最后一道生产工序。它是利用晶圆切割道上专门设计的测试结构进行电参数测试,以便监控晶圆制造过程和工艺偏差。Keysight 的4080B,P9000A等产品更是被广泛应用,是监测把控Foundry工艺稳定的最重要一环。

04、设计厂商收到回片后,需对芯片进行功能性和一致性测试,这也是芯片测试中非常重要的一环,需要测试的项目非常的多。

• 对高速数字芯片,需要用UXR示波器测量Tx性能,用任意波形发生器或者高速误码仪M8040A测量芯片的Rx性能,以及进行压力测试等,不同的高速接口和总线类型,比如以太网,PCIe,CXL,MIPI,USB,HDMI,DP等,都需要配合自动化测试软件进行一致性测试;

• 对射频与SoC芯片,需要用频谱仪比如UXA测量芯片的发射机性能,解调等,用矢量信号发生器比如MXG测量芯片的接收机性能,用信道仿真仪进行收发信机在不同信道条件下的表现,用基站模拟器UXM进行SoC芯片的射频,链路与协议测试;

• 对宽禁带半导体,需要用B1500A或者B1505A进行IV/CV等静态参数测试,用PD1500A或者PD1550A进行DPT动态参数测试;

• 对模拟芯片,进行电源完整性以及一般性的功能性测试,需要用到电源仿真,示波器以及自动化软件等。

算力芯片高速互联与电缆测试挑战

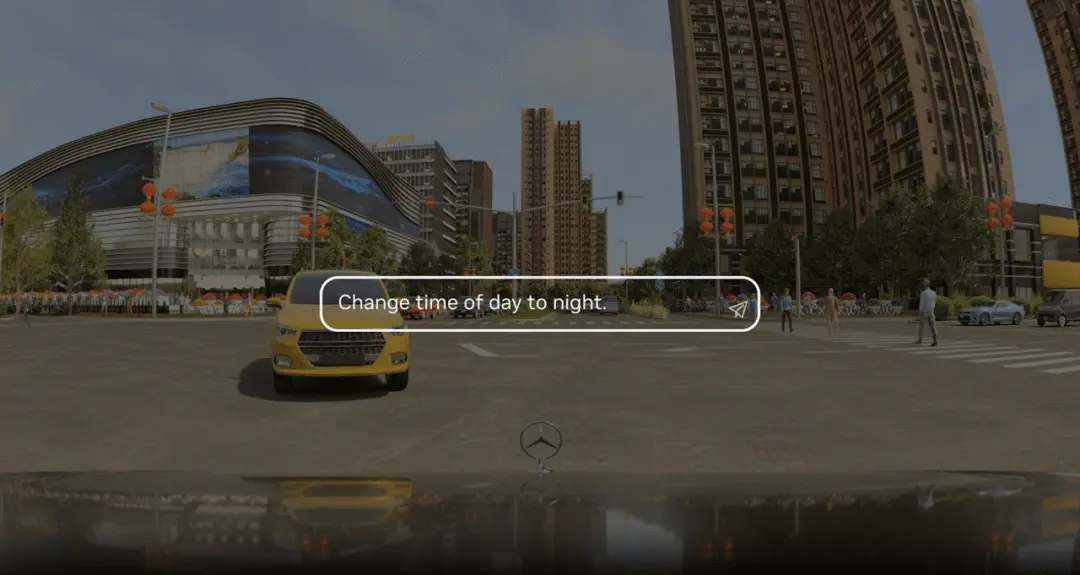

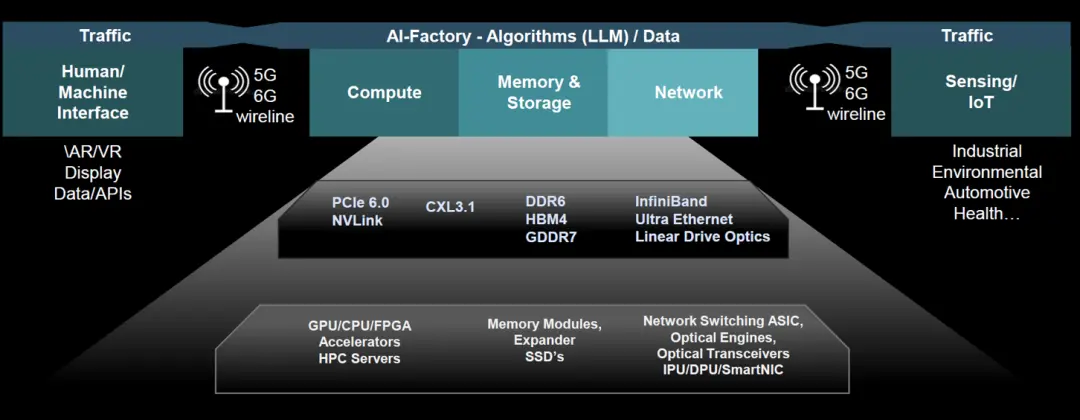

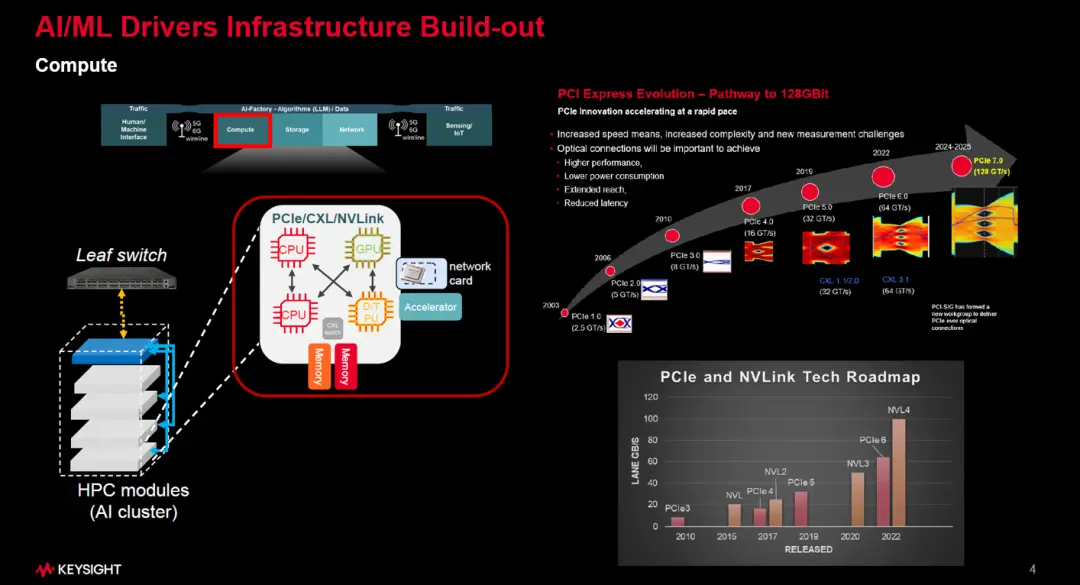

人工智能技术发展到今天,已经从单纯的计算、训练和推理工具,发展成为基础设施的一部分。如下图,无论是人机接口产生的数据还是传感器采集的数据都会通过无线或有线网络汇聚到AI数据中心,在这里借助大模型等算法进行处理,完成特定功能。

图:新一代的通信,计算,互联一体化基础设施

从上图可以看出算力基础设施有三个关键技术即计算,存储和网络技术。计算技术主要是PCIe和NVlink,实现芯片间级联,提升计算算力。采用该技术的主要是CPU/GPU/FPGA和各种定制化的ASIC等大芯片。存储技术主要是FLASH和DRAM,采用该技术的主要是NAND,DDR,LPDDR、HBM、GDDR等。网络技术涉及Ethernet、Infiniband。以太网是广泛使用的技术标准,协议栈复杂,也在通过RDMA和RoCE技术进行性能优化。IB网络主打高性能、低时延。目前行业领军企业成立了超级以太网联盟即UEC,致力于开发开放、高性能、满足AI要求的通信技术。使用Ethernet和IB技术的包括各种定制化的DPU,IPU,SmartNIC等产品。

以对算力要求最大的云端训练芯片为例,单颗芯片不足以支撑算力的需求,一般都采用异构架构即CPU+GPU,通过高速计算总线PCIe、NVlink等互联,将多个算力芯片及中央处理芯片互联,以形成更强大的算力供应,我们以公开资料收集的Nvidia的GB200 NVL72的架构为例:

1.Nvidia定义了超级芯片组Bianca board,每个芯片组由1个基于ARM架构开发的CPU和2个Blackwell架构的GPU芯片组成。

2.2个超级芯片组,即2 * CPU + 4 * GPU,构成一个compute tray,以1U的形态,直接插接在机框上,是日常部署、运维的最小化单元;而CPU和GPU之间,GPU和GPU之间,采用NVlink高速总线互联。

3.NVL72的一个机柜,一共有18个compute tray组成,即总共有18 * 4 = 72颗GPU。GB200 NVL72的NVlink在内部形成了一个全互联的状态,仅通过NV switch一跳,可以实现72颗B200 GPU的全互联。每个switch chip有4个NVlink端口,每个端口有72条铜缆对接,整个机柜有多达5000条铜缆互联。

我们把一个异构架构抽象出来,参考如下图,CPU/GPU/DPU/TPU之间,通过诸如NVlink(私有协议)或者PCIe(公有协议)这样的高速总线进行互联,以达到算力增倍的目的。互联总线的速率与日俱增,比如传统的PCIe总线,速率每3年就要翻一番,而即使这样的迭代速率,也难以满足算力要求的瓶颈,但是越来越高的传输速率,伴随着更加复杂的调制方式,对测试端的挑战也越来越高,举个例子,定稿于2022年的PCIe 6标准,最高速率达到64 GT/s,并且第一次采用了PAM 4的调制方式,而PCIe 7标准的速率更是高达128 GT/s,对测试平台的硬件和自动化测试的软件,都是个巨大的挑战。

图:异构架构的芯片间互联总线

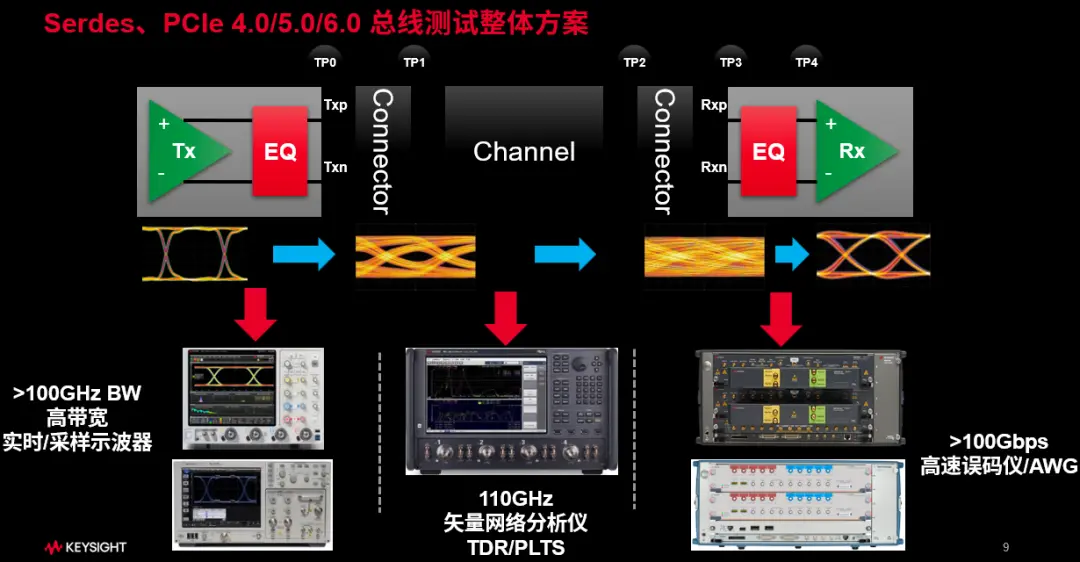

是德科技针对越来越苛刻的高速总线测试,提供了一套完整的测试平台,包括硬件与一致性软件。我们依然把对高速总线的测试,抽象为下图,对高速总线和接口的测试,一般包括发射机Tx测试,接收机Tx测试,链路测试。

图:数字芯片接口与高速总线测试

1.对发射机测试,一般用高速示波器,测量输出信号的眼图,抖动等指标。芯片端测试电信号指标定义在TP0测试点,TP0通常无法探测,可以选择在TP1采集信号通过去嵌方式实现。

2.对接收机测试,一般用高速误码仪,或者任意波形发生器,产生一个带压力的信号,输入到芯片端,用来检测接收机在不同噪声,串扰和信道条件下的性能。

3.信道或者链路测试,通常用网络仪,或者物理层测试系统,对S参数等指标进行测试。

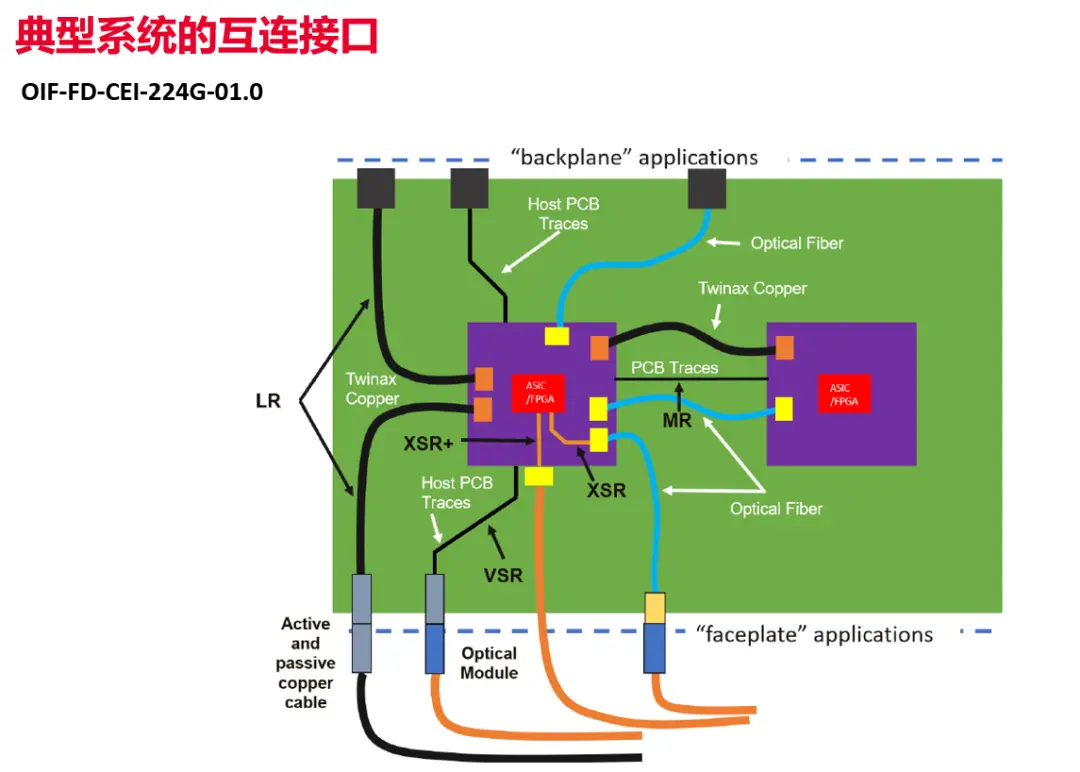

现在的算力服务器,例如GB200 的NVL72架构,也大量采用了铜缆作为互联接口,我们以OIF的互联接口定义举例,如下图:

图:OIF定义的互联接口,黑色标识为电缆/PCB标准

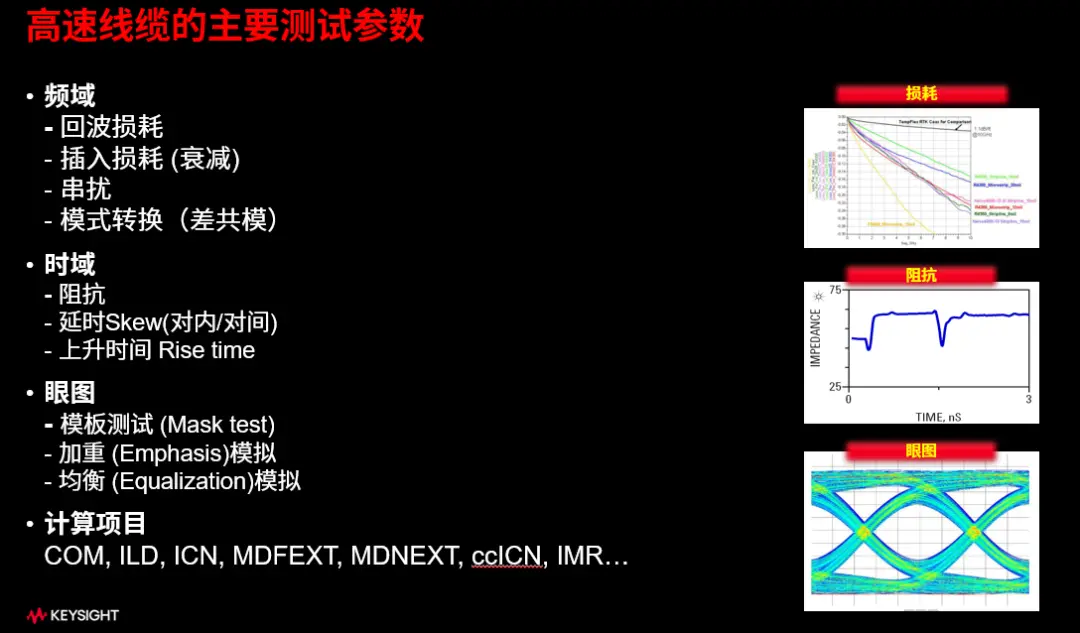

传统线缆的测试以频域S参数和时域特性阻抗为主,而要求能满足100G/200G电缆的测试,除了传统的频域和时域参数,还需要对眼图、误码率、COM等进行测试和计算,如下图:

图:高速电缆测试项目汇总

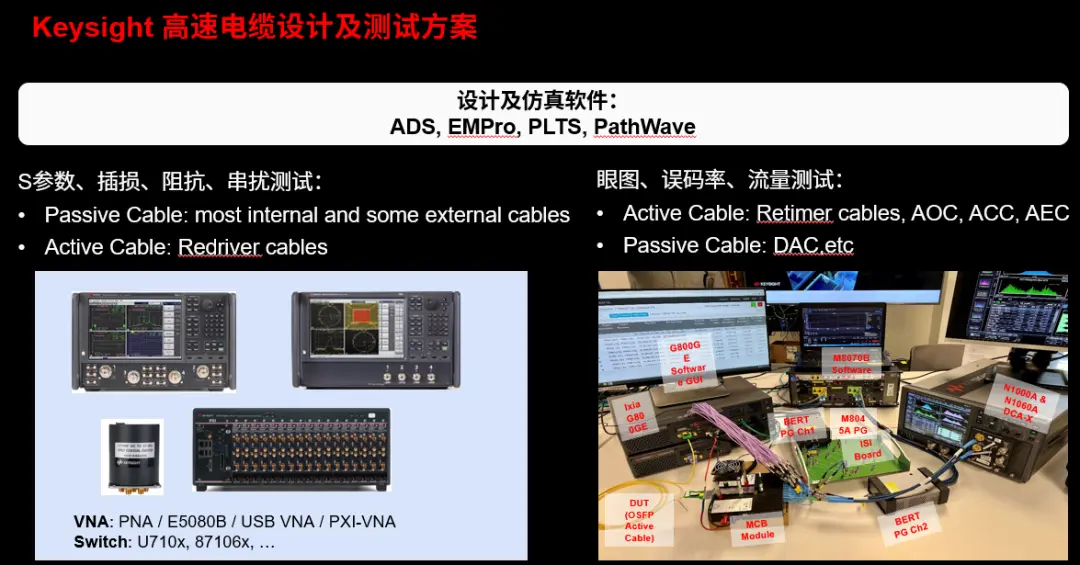

是德科技对高速线缆的各类参数,也提供了完整的解决方案,设计与仿真,可以采用ADS/EMPro做信号完整性的仿真测试。对S参数,阻抗,串扰等,研发级测试,一般采用PNA-X系列高性能网络仪,大规模生产测试,可以采用PXI架构的多端口网络仪来进行。眼图,误码率等指标,用高速示波器配合误码仪来完成。

图:是德科技对高速线缆测试提供了从仿真到测试的完整解决方案

“芯科技”科普视频

2024年,我们新上线了全新的短视频栏目“芯科技”系列,旨在以轻量化科普的方式,介绍目前业界最新的芯片技术,第一季,我们介绍了ChatGPT,GPU,异构总线等技术;第二季,我们会继续介绍包括Chiplet等技术,敬请期待!如果您有想观看的内容,也可以评论区告诉我们。

2024年是德科技在半导体行业参加的重要活动

4月17日

是德科技联合上海集成电路技术与促进中心,张江高科集团,共同举办了芯片新技术与测试峰会,我们与客户一起,探讨了包括算力芯片关键技术,以太网与高速总线测试,汽车芯片与MIPI A-PHY标准组进度,功率半导体测试等内容。

4月25日

厦门国家“芯火”双创基地(平台)-厦门集成电路设计公共服务平台联合是德科技举办芯片新技术与测试研讨会,以“技术研讨+实验室参观+交流”的形式,紧抓行业脉动与前沿技术,内容涵盖了AI人工智能、大模型等技术背后的算力芯片与互联技术、光芯片与光互联技术、RFIC/MMIC的On-wafer测试技术等。

9月25-27日

是德科技参加了在无锡召开的2024中国集成电路设计创新大会暨第四届IC应用展(ICDIA-IC Show),是德科技展示了基于UXR和M8040A的高速数字芯片测试平台。

10月16日

是德科技参加了在深圳举办的湾区半导体全产业链生态博览会(SEMiBAY),是德科技携最新的半导体曲线分析仪B1505A与测试机台,赞助并参与了AI芯片与高性能计算(HPC)应用论坛。

12月11日

是德科技还将参加上海集成电路2024 年度产业发展论坛暨中国集成电路设计业展览会ICCAD-Exp0 2024,除了带来我们最新的测试平台,我们还将对热门的算力芯片设计和测试技术进行现场直播,时间12月11日,下午14:00-15:30,C49-C50展位,欢迎您来共话芯片测试未来!更多信息详见本期副条文章“是德科技参加ICCAD Expo 2024”。

编辑推荐

最新资讯

-

全国汽车标准化技术委员会汽车节能分技术委

2025-04-18 17:34

-

我国联合牵头由DC/DC变换器供电的低压电气

2025-04-18 17:33

-

中国汽研牵头的首个ITU-T国际标准正式立项

2025-04-18 17:32

-

为什么要进行汽车以太网接收测试?汽车以太

2025-04-18 17:26

-

产品手册下载 | NI 全新USB数据采集-NI mio

2025-04-18 16:39

广告

广告