AEC-Q100标准对车规级芯片的要求

1.什么是AEC-Q100

2.AEC-Q100标准测试内容

3.AEC-Q100适用范围

4.AEC-Q100认证流程

1.什么是AEC-Q100

汽车电子协会AEC(Automotive Electronics Council)由克莱斯勒、福特和通用汽车等公司发起,并于1994年创立。

AEC-Q100则是汽车电子协会AEC制定的第一个车规级芯片验证标准。其全称为:Failure Mechanism based Stress Test Qualification For Integrated Circuits,基于失效机制的集成电路应力测试标准。

AEC-Q100主要针对车载应用的集成电路IC产品(Integrated Circuits)所设计,是一套应力测试标准,旨在通过严格的测试流程,确保芯片在复杂多变的汽车环境下具备高可靠性、高安全性和高稳定性。

Q100的初版在1994年6月提交给了所有的IC供应商,当前最新版本为2023年8月11日发布的AEC-Q100-REV-J版本。

2.AEC-Q100测试内容

AEC-Q100除了AEC-Q100-REV-J这个主标准(base document)外,还有10个分标准,分别是:

2.1、AEC-Q100-001-Rev-C: Wire Bond Shear Test封装打线强度试验

芯片进行封装时,需要利用金属线材,将芯片(Chip)及导线架(Lead frame)做连接,由于封装时,可能有强度不足与污染的风险。此试验的目的,即为藉由打线拉力(Wire Bond Ppull)与推力(Wire Bond Shear)来验证结合能力,确保其封装可抵抗外在应力。

2.2AEC-Q100-002-Rev-E: Human Body Model (HBM) Electrostatic Discharge Test人体模型(HBM)静电放电测试

HBM测试模拟了人体通过接触或近距离放电到IC上的情况。在测试中,使用标准化的电荷传递模型和波形,以评估IC在不同电荷水平下的耐受能力。

放电电流的大小和波形是HBM测试的重要评估指标。放电电流的大小通过测量电路模型中的电阻两端的电压来计算,而放电电流的波形则通过示波器来观测。测试时需要进行多次放电,以获得放电电流的统计数据,从而评估器件的静电放电敏感度。

2.3、AEC-Q100-004-Rev-D: IC Latch-Up Test集成电路闩锁效应测试

闩锁效应是指在集成电路中,由于两个相反极性的晶体管(PNP和NPN)形成一个正反馈回路,导致电路失去控制,出现异常电流流过的现象。这种异常电流可能会损坏芯片或导致电路功能失效。闩锁效应通常发生在CMOS集成电路中,特别是当电路设计密度较高、电压或电流的瞬间变化较大时。 IC Latch-Up Test的主要目的是验证集成电路在特定应力条件下是否会发生闩锁效应。通过测试,可以评估集成电路的可靠性,并确保其在实际应用中能够稳定运行。

2.4、AEC-Q100-005-Rev-D1: Non-Volatile Memory Program/Erase Endurance,Data Retention,and Operational Life Test非易失性存储器程序/擦除耐久性,数据保留和操作寿命测试

2.4.1、程序/擦除耐久性测试(Endurance Test)的目的是评估非易失性存储器NVM在连续多次数据重写(编程/擦除循环)后的性能稳定性。

测试方法:

(a)对NVM的指定地址进行反复的置位/复位操作,执行一定数量的操作循环;

(b)每个循环包括写入和擦除两个操作,写入操作使用芯片规范的写入脉冲电压和持续时间,擦除操作使用芯片规范的擦除脉冲电压和持续时间;

(c)在操作循环执行到一定次数时(如10⁴次、10⁵次等),对每个存储单元测量其电阻值或读取状态,并与初始值进行比较。

评估标准:

存储单元的电阻值或读取状态在多次循环后应保持稳定不变。 成功执行写入/擦除循环的次数越多,表明NVM的耐久性越好。

2.4.2

数据保留测试(Data Retention Test)的目的是评估NVM在长时间未进行读写操作后,存储单元保持数据的能力。

测试方法:

(a)将NVM的所有存储单元置为特定状态(如全部置为1或0);

(b)在规定的时间内(如室温下保存500小时、高温下保存100小时或更短时间等),定期对存储单元进行读操作,记录读取电压、读取电流以及读取状态。

评估标准:

存储单元的读取电压、读取电流以及读取状态在长时间内应保持稳定不变。 出现明显变化(如读取电流、电压变化超过一定阈值)的存储单元数量越少,表明NVM的数据保留能力越强。

2.4.3、操作寿命测试(Operational Life Test)的目的是综合评估NVM在实际使用过程中的性能稳定性和寿命。

测试方法:

(a) 模拟NVM在实际应用中的读写操作模式,进行一定次数的读写循环;

(b)在测试过程中,定期监测NVM的性能指标(如读写速度、功耗、错误率等)。

评估标准:

NVM的性能指标在测试过程中应保持稳定或逐渐降低,但不应超出可接受范围。

达到预定测试次数(如10⁶次读写循环)后,NVM仍能正常工作的比例越高,表明其操作寿命越长。

2.5、AEC-Q100-007-Rev-B: Fault Simulation and Test Grading故障模拟和测试分级

故障模拟(Fault Simulation)是研究集成电路中相互作用参数之间关系的一种模拟过程,它定义了产品故障分级流程,并指定了被测器件的生产制造测试程序必须能够识别到的故障级别(不包括参数故障)。故障模拟的目的是使用当前的故障模拟模型开发,针对产品各功能模块的最佳故障覆盖率方案,以便最小化识别缺陷并向最终用户报告故障测试覆盖率程度。

测试分级(Test Grading)适用于所有数字电路,包括混合信号和线性电路的数字部分,但不适用于电路的线性部分。它涵盖了建模和逻辑仿真要求,假设的故障模型和故障模拟要求,以及评估和报告测试覆盖率必须遵循的程序。

在进行故障模拟和测试分级时,需要考虑到故障模型的质量,即故障模型是否充分模拟了制造过程中缺陷的影响,以及环境缺陷激活条件,即某些缺陷仅在某些激活条件(电压、温度、频率)下表现出来。 通过故障模拟,可以识别出潜在的故障点,并通过测试分级来评估这些故障点对整体电路的影响,从而采取相应的措施来提高电路的可靠性和稳定性。

2.6、AEC-Q100-008-Rev-A: Early Life Failure Rate (ELFR)生命早期故障(ELFR)

ELFR主要用于衡量产品在投入使用的初期阶段(如几个月内)的可靠性表现。通过ELFR测试,可以识别并排除由于制造工艺、设计缺陷或材料问题导致的早期失效产品,从而提高整体产品的质量和可靠性。

ELFR测试方法:

(a)样本选择:通常需要从至少三个不连续的产品批次中抽取样本进行测试,以确保测试结果的代表性;

(b)测试条件:测试环境通常包括高温、高电压等加速应力条件,以模拟产品在实际使用中的恶劣环境。测试时间根据具体产品的特点而定,但通常在48小时至168小时之间。

(c)测试过程:在测试期间,对被测产品施加最大工作电压(比额定工作电压高5%~10%),并监测其电气性能。测试结束后,在室温下进行电气测试以评估产品的性能是否满足要求。

ELFR的评估标准通常是“0失效”,即所有被测产品在测试期间均不应出现故障。如果出现故障,则需要采取纠正措施,如改变加工工艺、设计或采用更严格的老化设计等。

2.7、AEC-Q100-009-Rev-B: Electrical Distribution Assessment电分配

电分配要在室内、热、冷三种温度下进行测试。

本试验方法的目的是定义获得集成电路上电参数的表征、电分布和参数位移数据的方法。该方法的目的是评估零件在正常工艺变化、时间和/或预期应用环境(例如,工作温度范围、电压等)下在规范参数范围内的功能。

电分配测试:在给定的温度、频率和电压下,从正常批量产品中的随机提取的样品来进行电气参数的统计分布,以确定器件满足客户规范或供应商规格书中参数要求的能力。

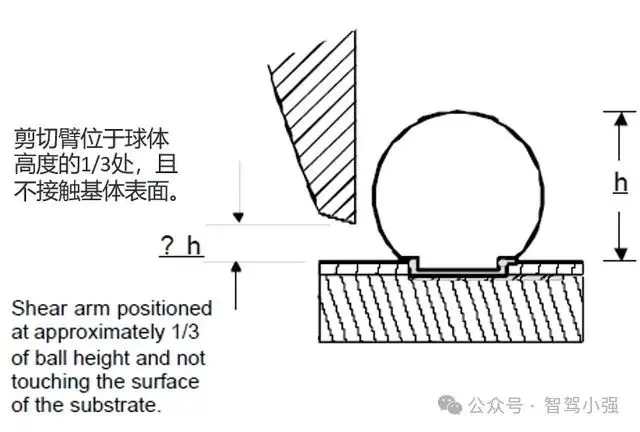

2.8、AEC-Q100-010-Rev-A: Solder Ball Shear Test焊球剪切试验

焊球剪切试验的主要目的是通过模拟实际工作条件下对焊接焊球施加的剪切力,来评估焊球与基板或封装之间的连接强度和质量。

(a)将测试样品放在干净的电路板或陶瓷片上,焊锡球朝上。使用回流炉或红外回流对样品进行加热预处理,回流峰值温度为220+5 /-0 °C,回流曲线按照J-STD-020定义(不需要潮湿暴露)。

(b)让样品冷却到室温(22±3°C)。

(c)将试样安装在剪切测试仪上,剪切臂放置在球高度的1/3处,且不接触基板表面,如下图所示,以恒定的剪切速率0.28 ~ 0.50 mm/s剪切球。记录抗剪强度。

(d)使用放大率不低于40倍的显微镜,检查并记录球分离模式。

2.9、AEC-Q100-011-Rev-D: Charged Device Model (CDM) Electrostatic Discharge Test带电器件模型(CDM)静电放电测试

CDM测试模拟的是电子元件在制造、运输或处理过程中因摩擦或其他因素而积累静电,并在随后与地或其他导体接触时迅速放电的现象,这种放电现象具有电流上升时间短、峰值电流高的特点。测试步骤如下:

(a)将待测IC放置在测试台上,并确保其引脚与测试设备的Pogo pin正确接触。

(b)设置测试参数,包括充电电压、放电波形等,根据所选的测试标准进行调整。

(c)启动测试设备,对待测IC进行充电,使其内部积累静电。

(d)当待测IC的引脚与接地导体接触时,触发放电事件,并记录放电波形和参数。 (e)对测试结果进行分析,评估待测IC在静电放电条件下的敏感度和可靠性。

2.10

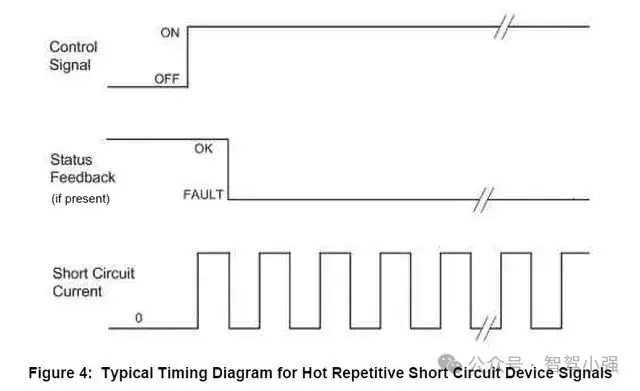

AEC-Q100-012-Rev-: Short Circuit Reliability Characterization of Smart Power Devices for 12V Systems 12V系统智能功率器件的短路可靠性测试

本规范的目的是验证在持续短路条件下产品“保护”功能的工作可靠性。

与短路操作有关的故障可能以两种方式发生:

(i)器件无法关闭(电气短路)

(ii) 器件无法开机(开路)

测试过程必须确保检测到两种失效模式。当检测到器件故障时,必须小心避免器件故障影响或损坏其他被测器件。

短路应力会导致被测器件物理性能的退化,从而导致电参数(如导通电阻)的偏移。因此,当常规(开/短路)故障无法在合理的测试时间内观察到时,超出规定限度的电气参数漂移可以用作替代失效准则。

每批次需要10个样品,来自三个不同的批次。测试通过的标准为:测试过程中不允许有任何失效发生。

3.AEC-Q100适用范围

AEC-Q100认证是芯片产品应用于汽车领域的基本门槛。获得该认证意味着芯片产品已经通过了严格的测试和鉴定,符合汽车电子系统的可靠性要求。

AEC-Q100标准适用于单颗IC芯片,包括但不限于MCU芯片、MPU芯片、存储类芯片、计算类芯片、安全类芯片、LED类驱动芯片、电源芯片、运算放大器、比较器、感知用模拟芯片、通信类芯片等。

这些芯片通常被广泛应用于汽车电子系统中,如发动机控制、车身控制、安全系统、信息娱乐系统、智能驾驶系统等。

AEC-Q100测试项目共计41项,分为多个群组,包括加速环境应力测试、加速生命周期模拟测试、封装组装完整性测试、芯片制造可靠性测试、电性验证测试、缺陷筛选测试和腔体封装完整性测试等。

这些测试项目涵盖了芯片产品的多个方面,从环境适应性、生命周期模拟到封装和制造可靠性等,以确保芯片产品在实际应用中的稳定性和可靠性。

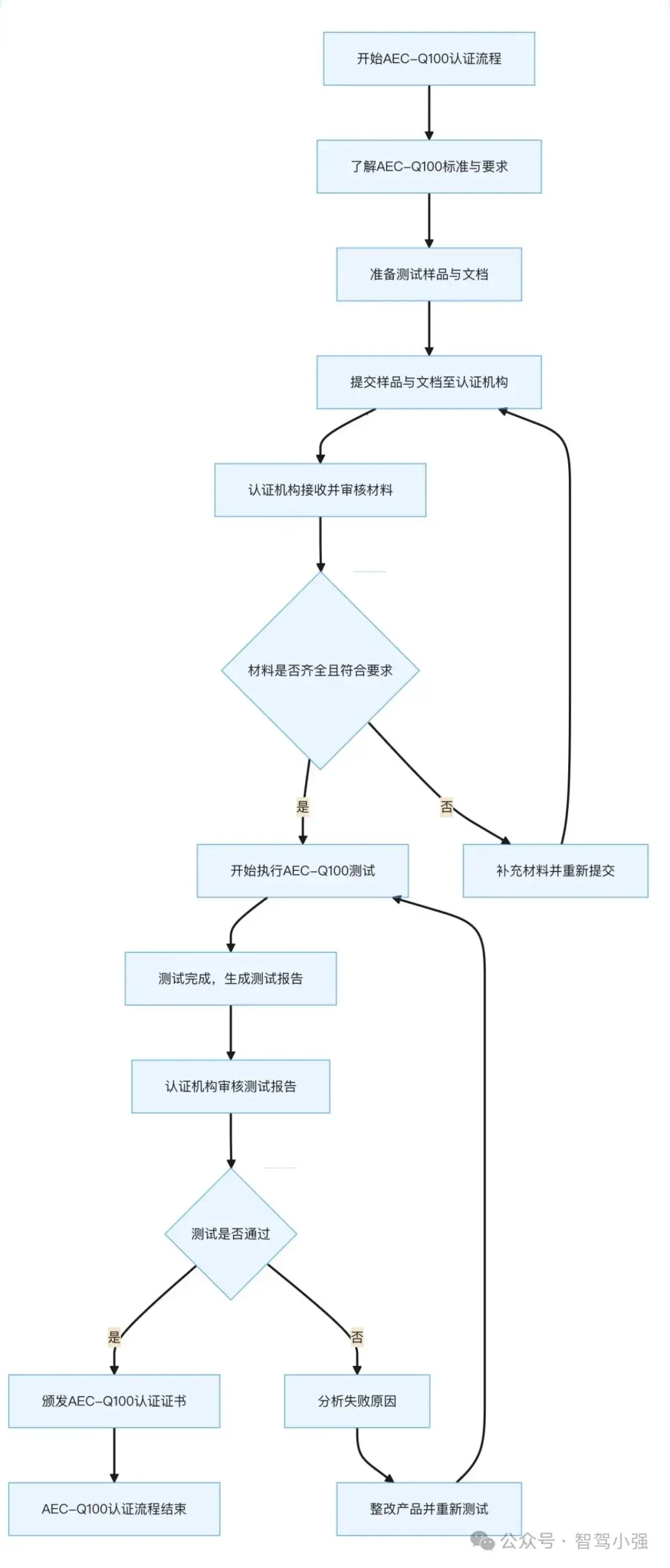

4.AEC-Q100认证流程

下图详细展示了AEC-Q100认证的整个流程,从了解标准与要求开始,到准备测试样品与文档,提交材料,执行测试,审核测试报告,直到最终获得认证证书或进行整改并重新测试。

认证的关键步骤包括:

了解标准与要求: 申请方需要详细了解AEC-Q100认证的标准和要求,确保产品符合相关规范。这包括熟悉测试项目、测试方法和合格标准等。

制定测试计划: 根据产品特点和认证要求,制定详细的测试计划和方案。测试计划应明确测试项目、测试方法、测试设备、测试条件以及测试人员等关键要素。

实施测试: 按照测试计划,在认证机构或认可的实验室进行各项测试。测试过程中应确保测试结果的准确性和可靠性,同时记录测试数据和结果以备后续审查。

提交申请与审核: 完成测试后,向认证机构提交测试报告和申请材料。申请材料通常包括产品说明书、技术资料、测试数据等。认证机构将对申请材料进行审核和评估,确保产品符合AEC-Q100认证的标准和要求。

获得认证: 如果产品符合AEC-Q100认证的标准和要求,认证机构将颁发AEC-Q100认证证书给申请方。认证证书是证明产品质量和可靠性的权威凭证,有助于提升产品在汽车市场上的竞争力。

国内的广电计量、广东优科检测认证有限公司、苏试宜特、SGS半导体及可靠性实验室均具备中国合格评定国家认可委员会(CNAS)认证的AEC-Q100测试资质。

编辑推荐

最新资讯

-

全国汽车标准化技术委员会汽车节能分技术委

2025-04-18 17:34

-

我国联合牵头由DC/DC变换器供电的低压电气

2025-04-18 17:33

-

中国汽研牵头的首个ITU-T国际标准正式立项

2025-04-18 17:32

-

为什么要进行汽车以太网接收测试?汽车以太

2025-04-18 17:26

-

产品手册下载 | NI 全新USB数据采集-NI mio

2025-04-18 16:39

广告

广告